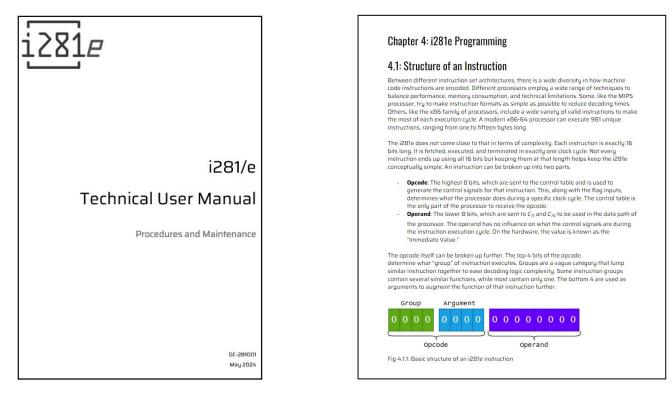

# 1281*P* [PU

#### Implement the i281 CPU in Hardware

Team Members:

Daryl Damman, Logan Lee, Grant Nordling, Braxton Rokos, Gavin Tersteeg Client/Advisor: Professor Alexander Stoytchev

#### **Project Vision**

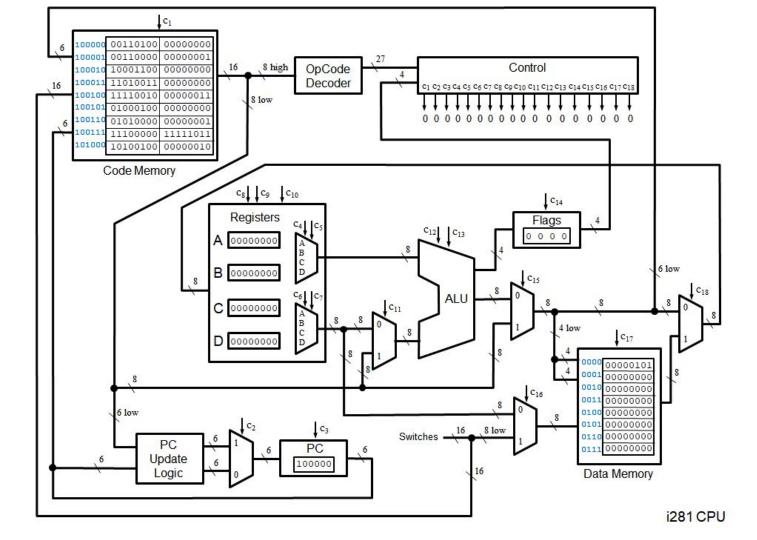

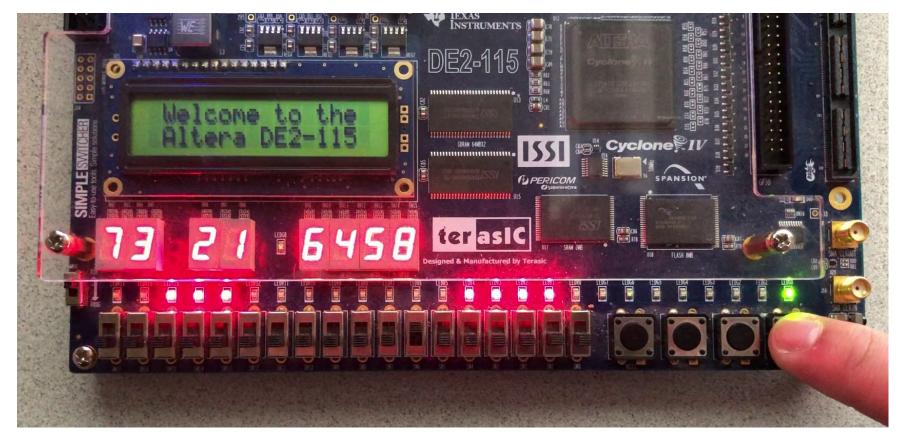

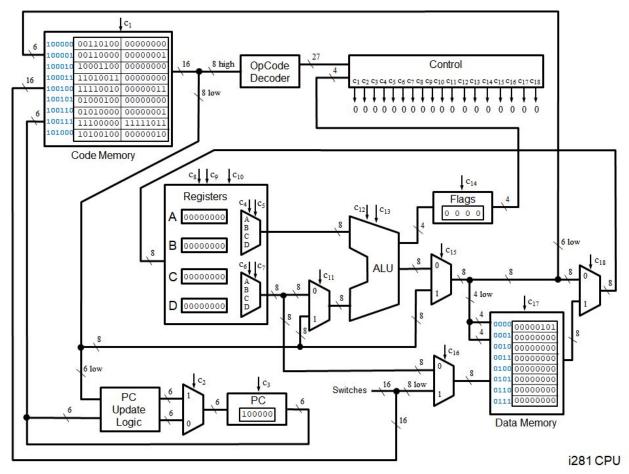

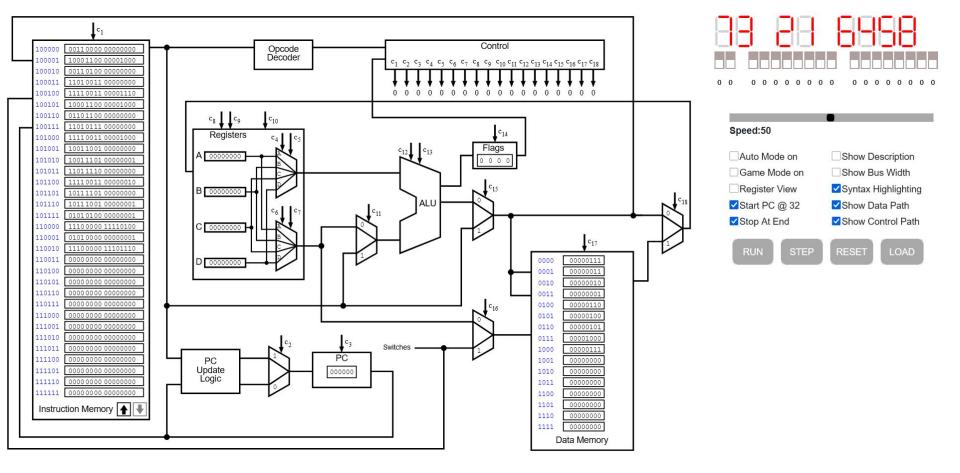

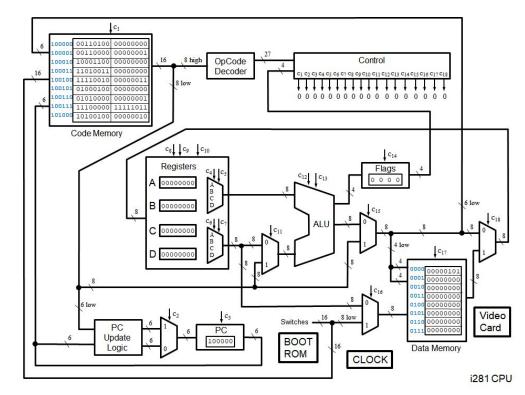

The i281 CPU was designed to support the curriculum in CprE 281: Digital Logic. Currently, this design is implemented to run on an FPGA and a web simulator. To fully realize the potential of this teaching tool, students also need a physical implementation to interact with.

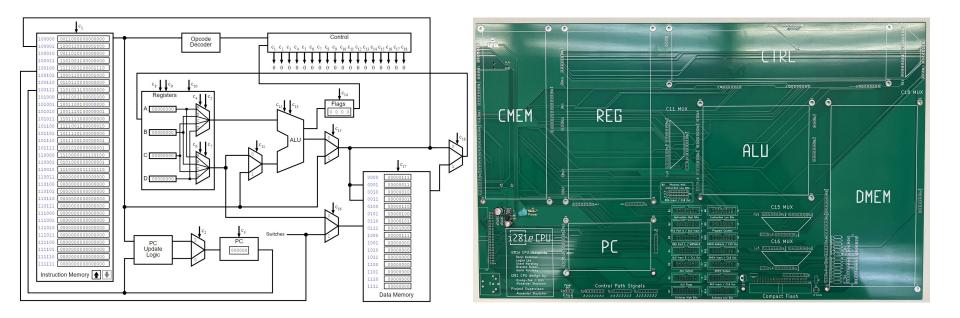

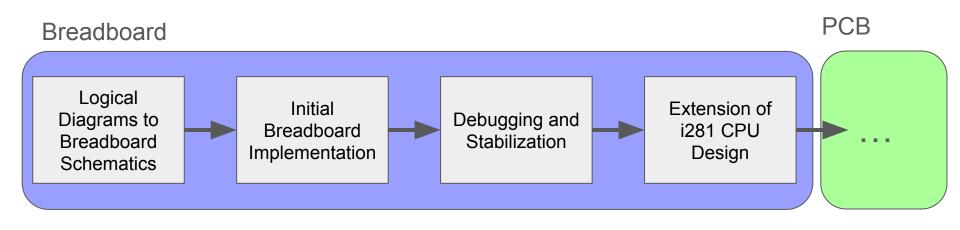

Our implementation of the i281 CPU must be created in dedicated hardware and remain similar to the FPGA and simulator designs. Two implementations must be designed on breadboards and printed circuit boards, respectively.

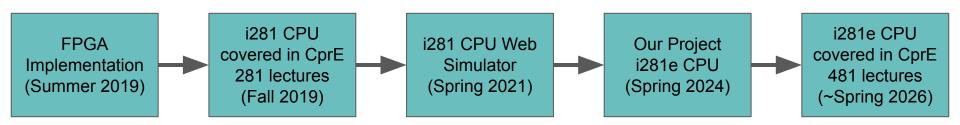

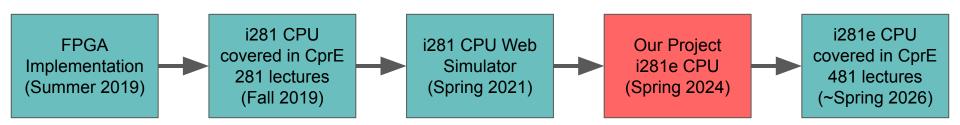

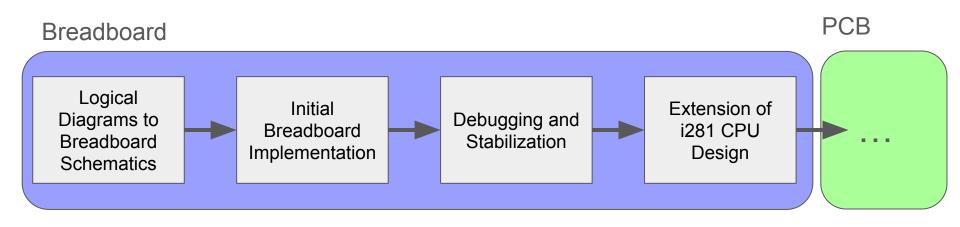

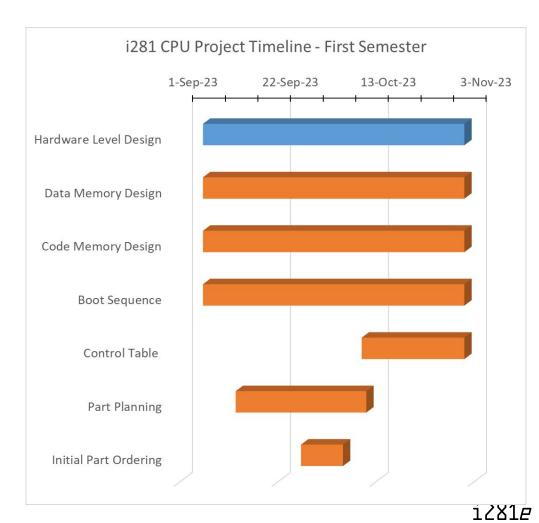

#### **Historical Timeline**

#### **Historical Timeline**

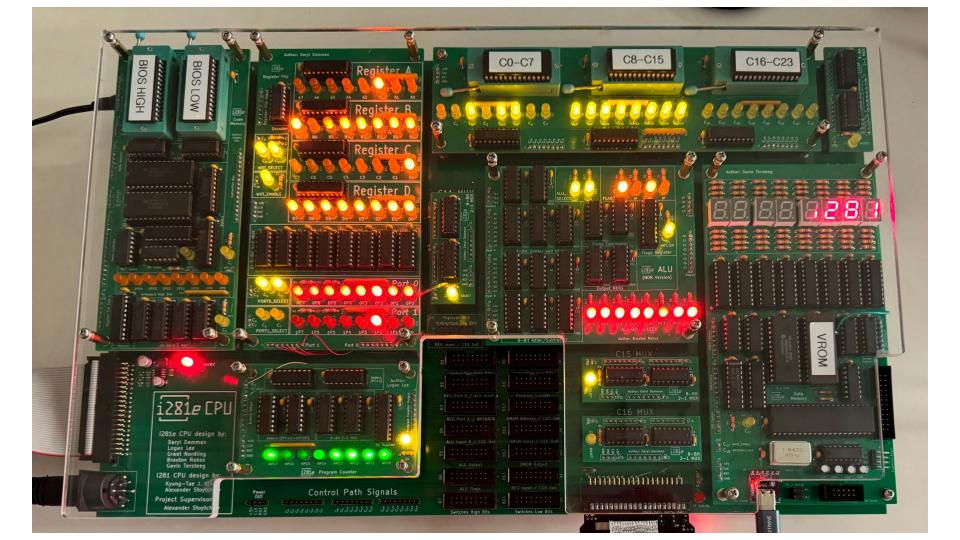

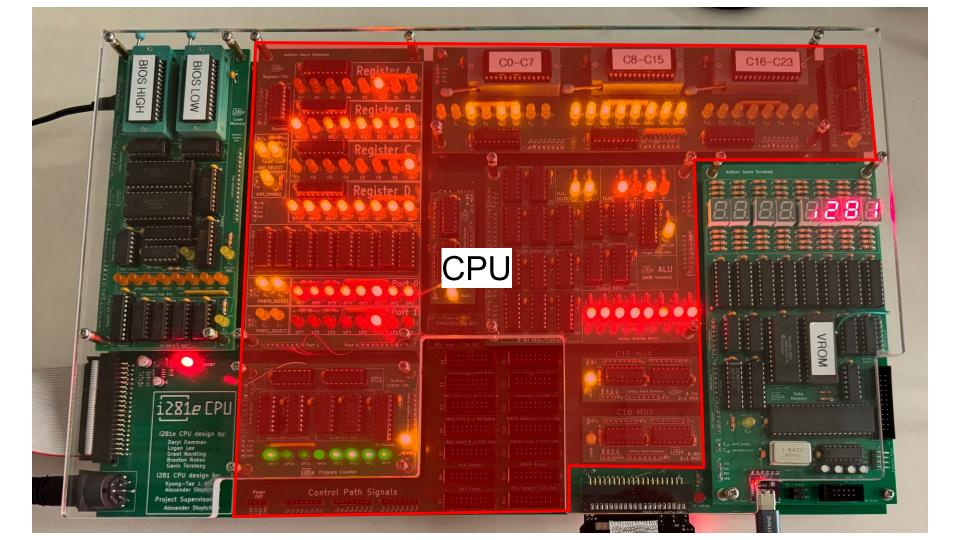

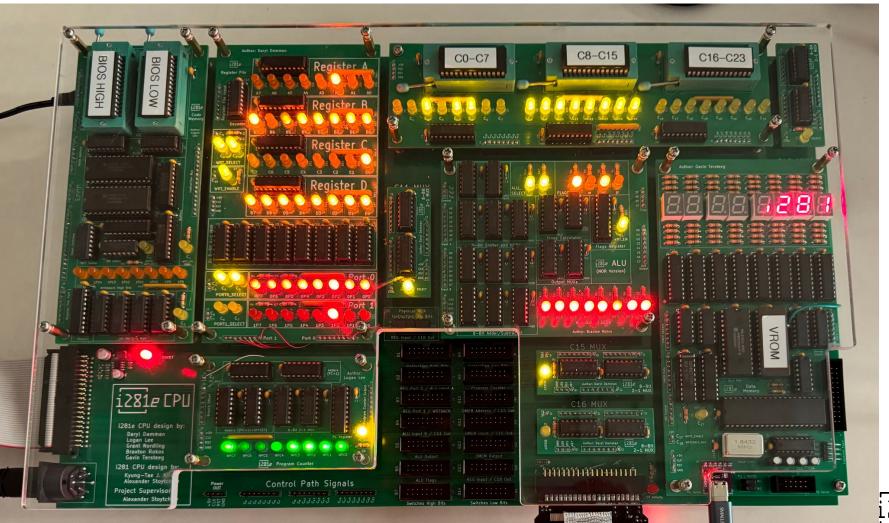

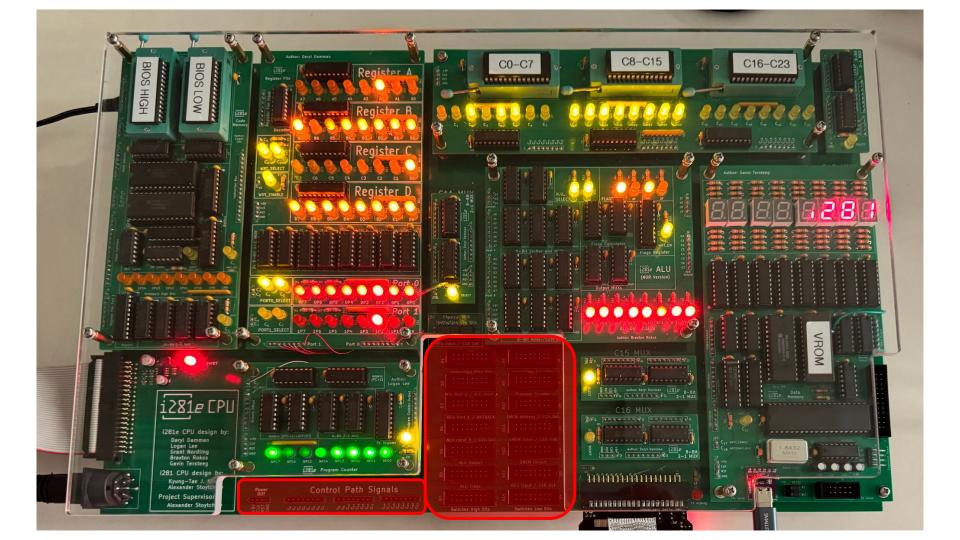

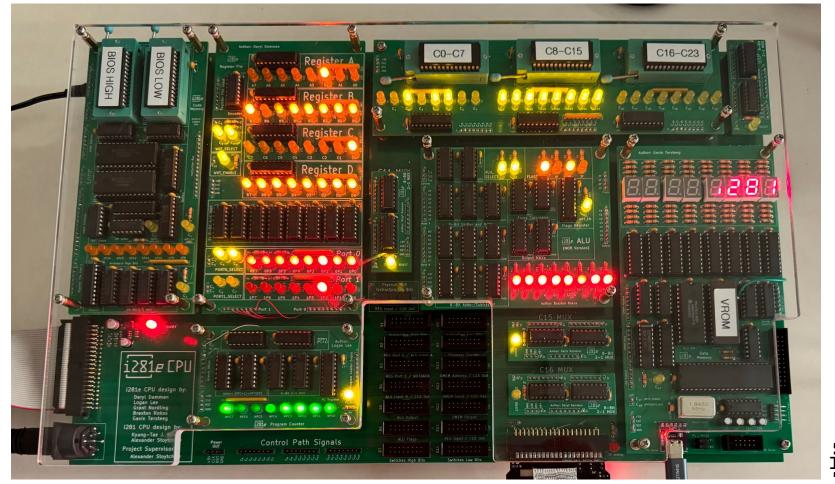

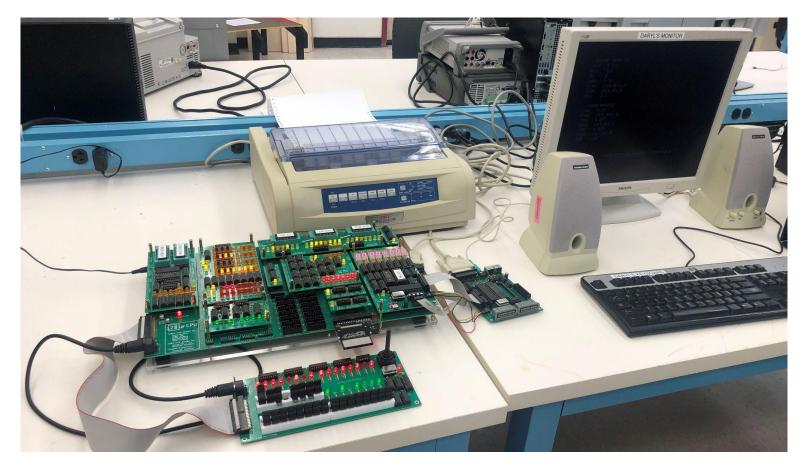

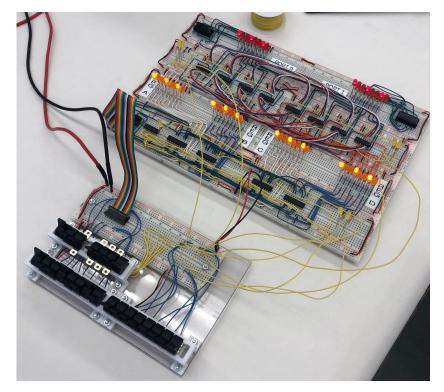

#### **Fully Functional Prototype**

i281*e*

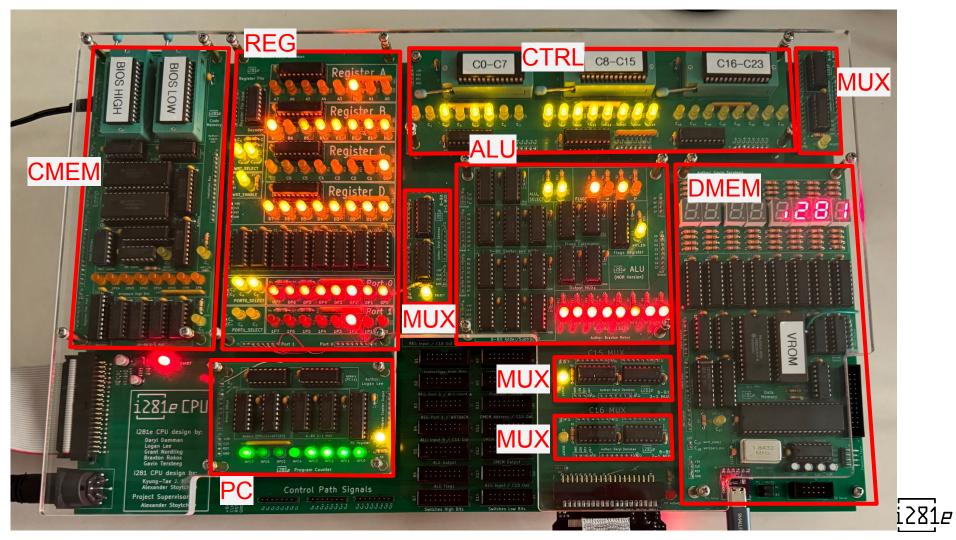

#### i281e CPU Specifications

- Clock Speed: 1Hz up to 2MHz (up to 2.5MHz overclock)

- Processor fails around 2.75MHz

- Power Requirements: 0.8A @ 5VDC (Input 5-12VDC)

- Fuse for overcurrent protection @ 2A

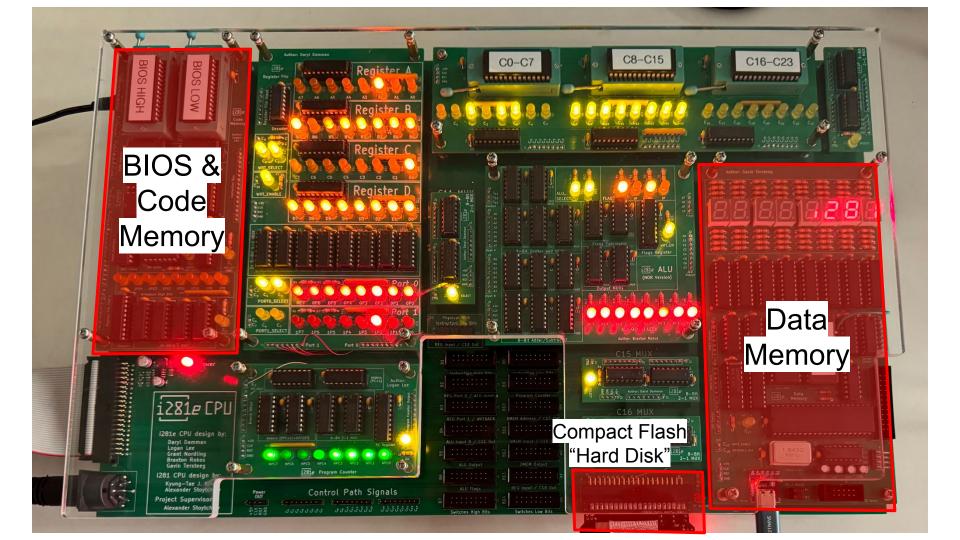

- Memory: 32 KW (64 KB) of Code RAM, 32 KB of Data RAM

- Also includes 128 words of Code ROM for booting the system

- Compact Flash: extended memory for long-term storage

- Acts as the "hard disk" and stores the OS and File System for DOS/281

### Requirements

Braxton Rokos Electrical Engineering

#### **Project Requirements**

- The CPU must be explainable to sophomore students in CprE 281.

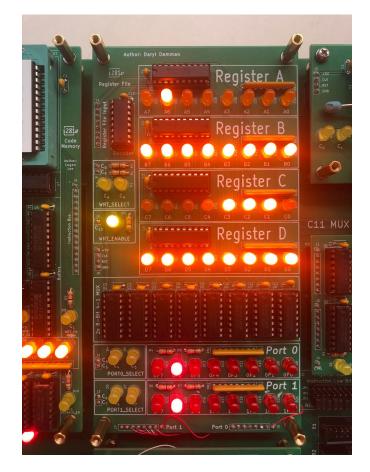

- The CPU data path and control path must be visualized with LEDs.

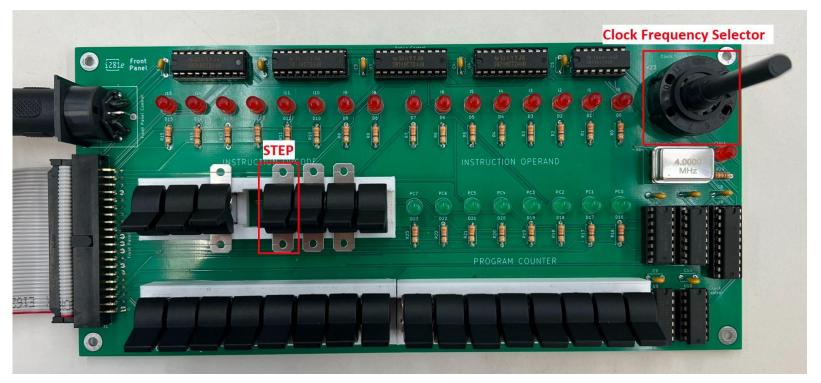

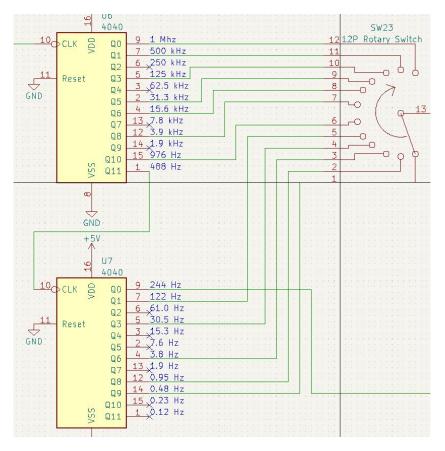

- Adjustable CPU clock to enable stepping through individual instructions and operating at different clock frequencies.

- The CPU must be capable of playing the original i281 PONG video game and other example programs from the FPGA and the Web Simulator.

- The CPU design must be as close as possible to the original design.

- It must look cool.

#### **Explainable Content**

The CPU must be explainable to sophomore students in CprE 281.

#### **Visualization**

The CPU data path and control path must be visualized with LEDs.

#### **Visualization**

The CPU <u>data path</u> and control path must be visualized with LEDs.

#### **Visualization**

The CPU data path and <u>control path</u> must be visualized with LEDs.

#### **Adjustable Clock**

Adjustable CPU clock to enable stepping through individual instructions and

operating at different clock frequencies.

#### **Example Programs**

The CPU must be capable of playing the original i281 PONG video game and other example programs from FPGA and Web Simulator.

#### **Design Similarity**

The CPU design must be as close as possible to the original design.

# It must look cool

## **Design Process**

Daryl Damman Software Engineering

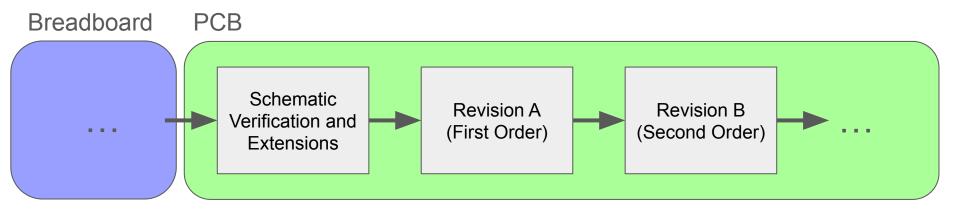

#### **Design Iterations**

#### **Design Iterations**

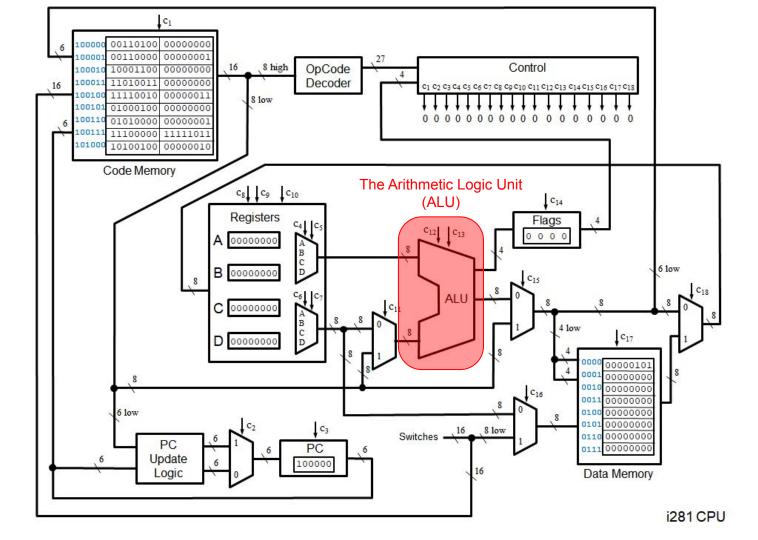

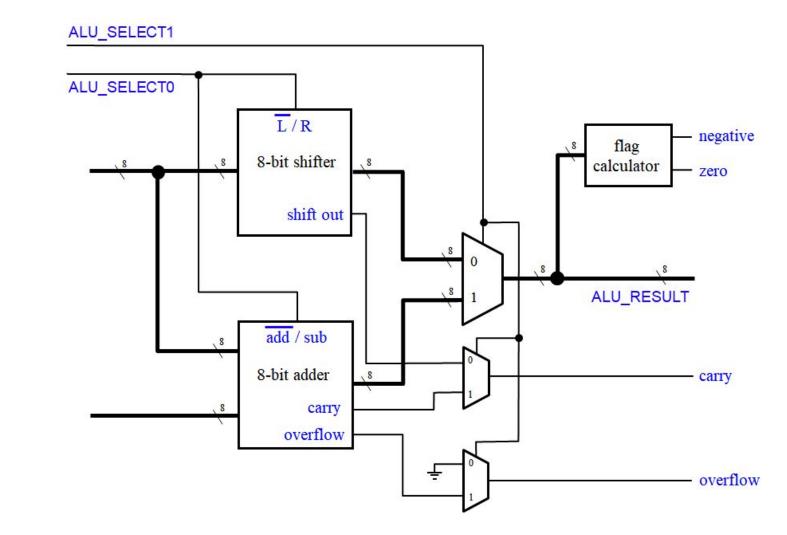

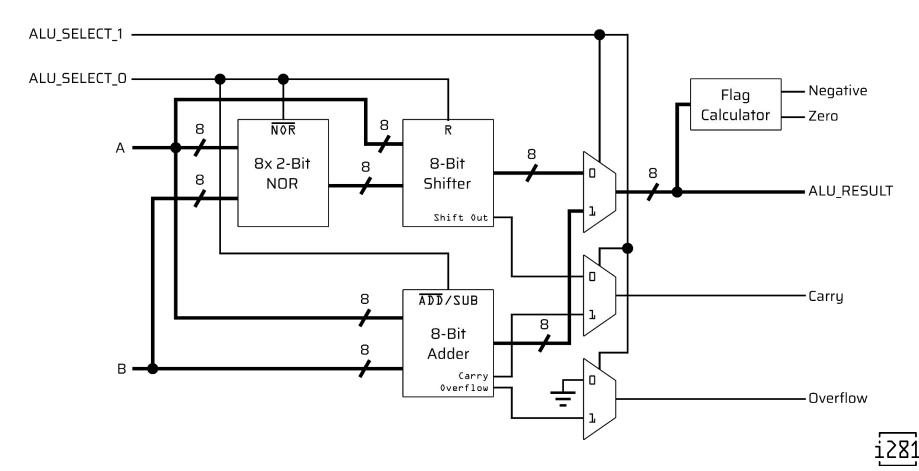

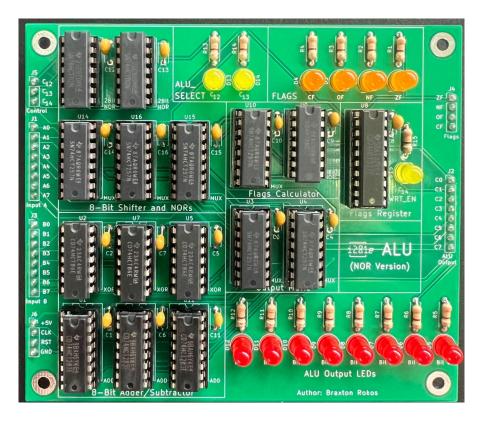

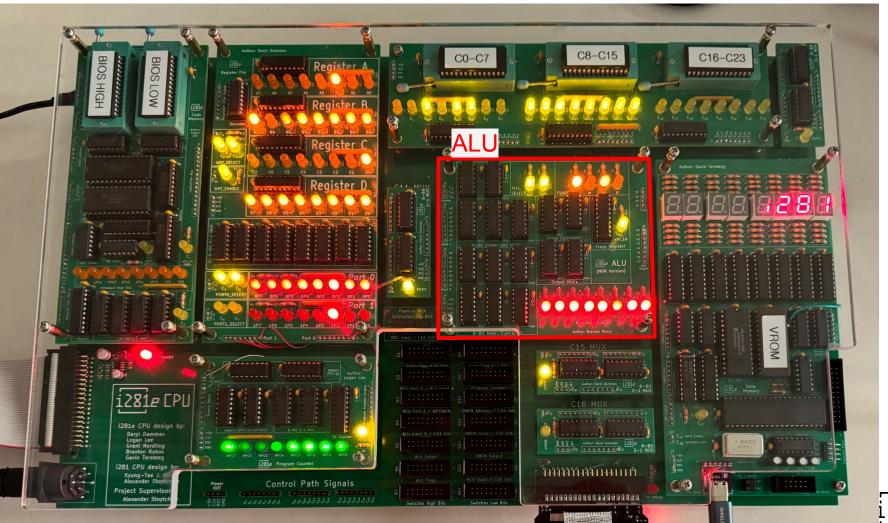

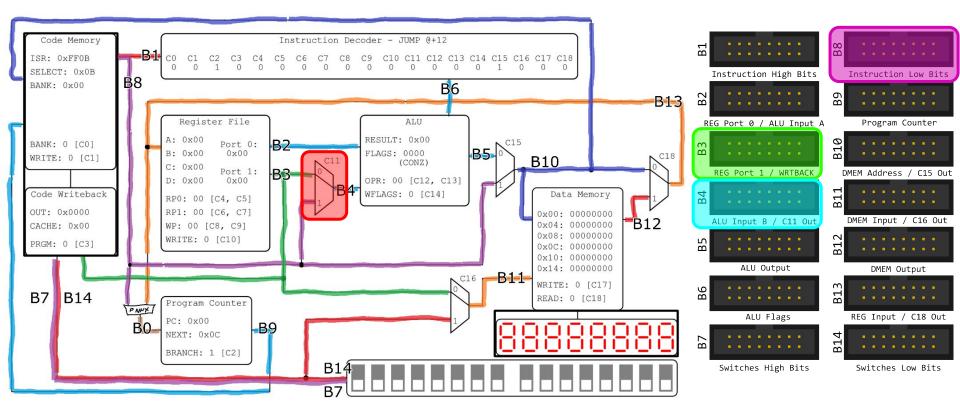

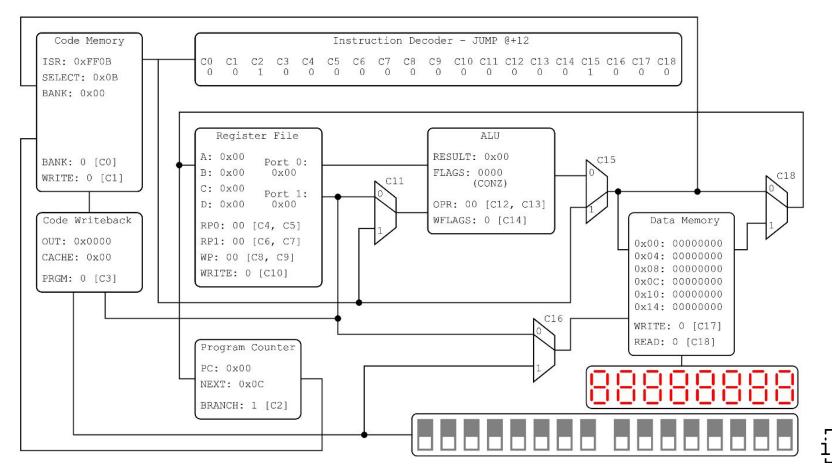

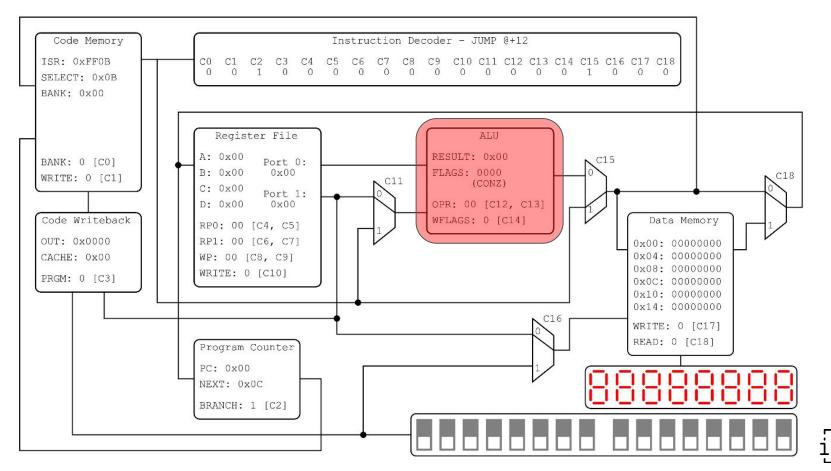

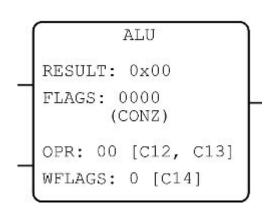

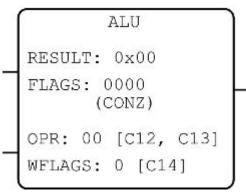

#### Let's look at the Arithmetic Logic Unit (ALU) as an example.

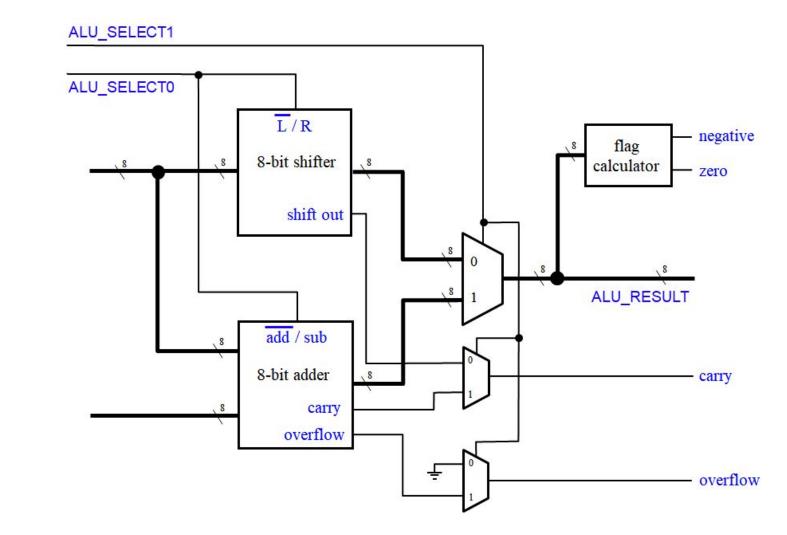

#### **ALU Logic**

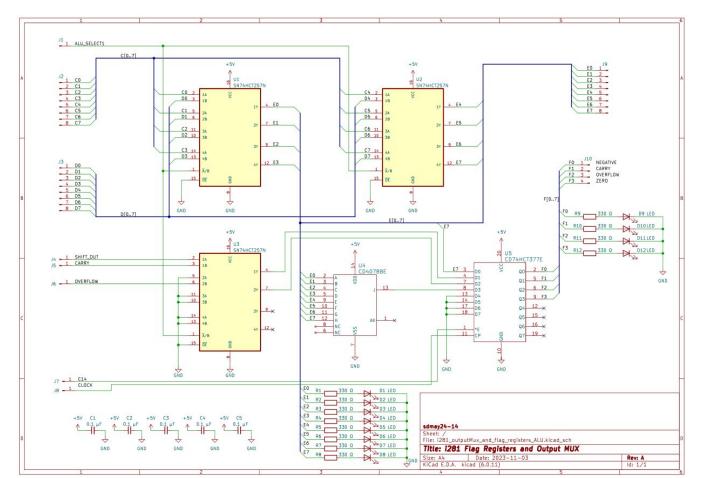

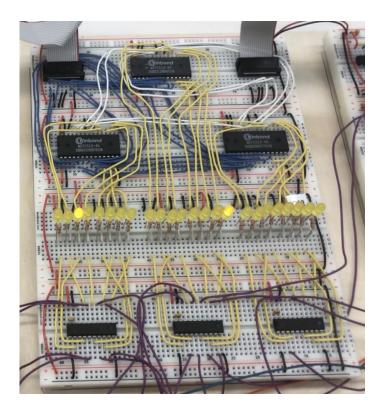

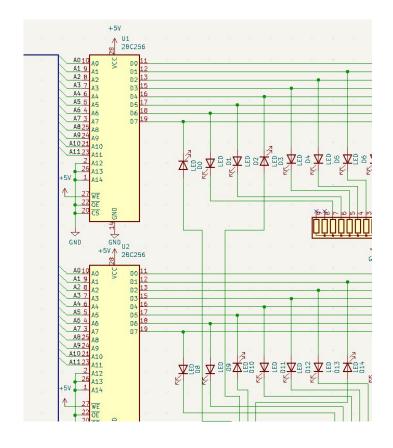

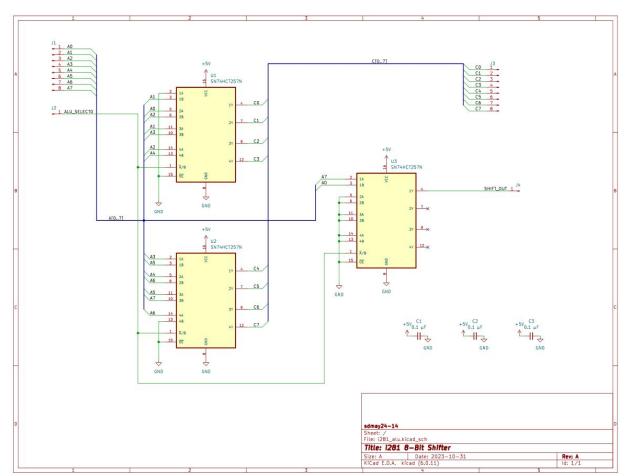

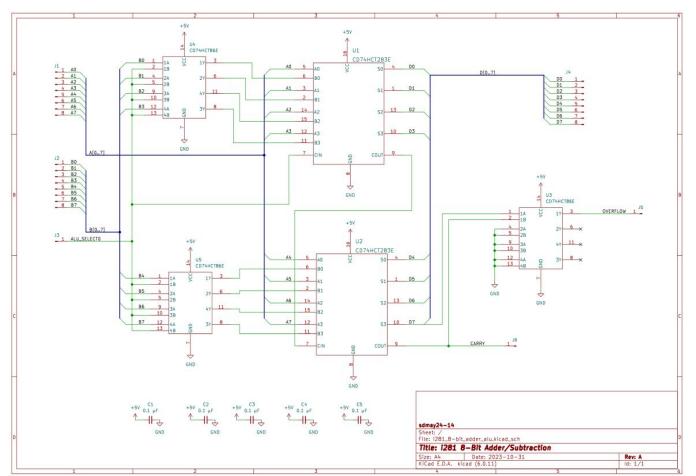

#### **ALU Schematics**

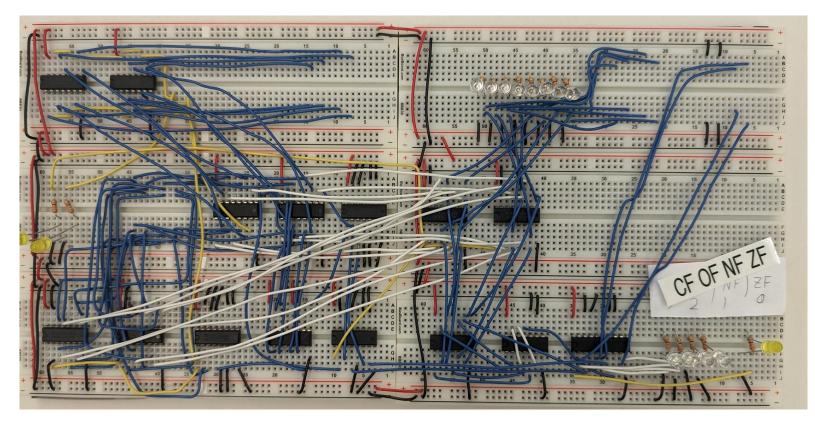

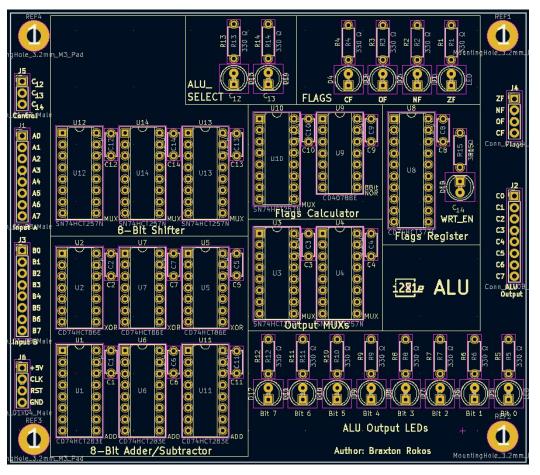

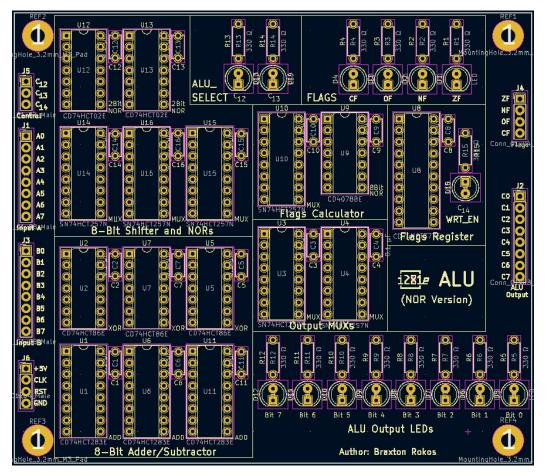

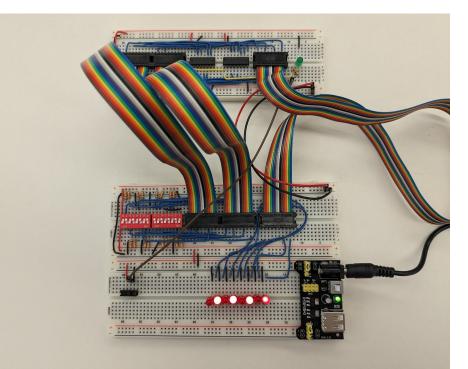

#### **ALU Implementation**

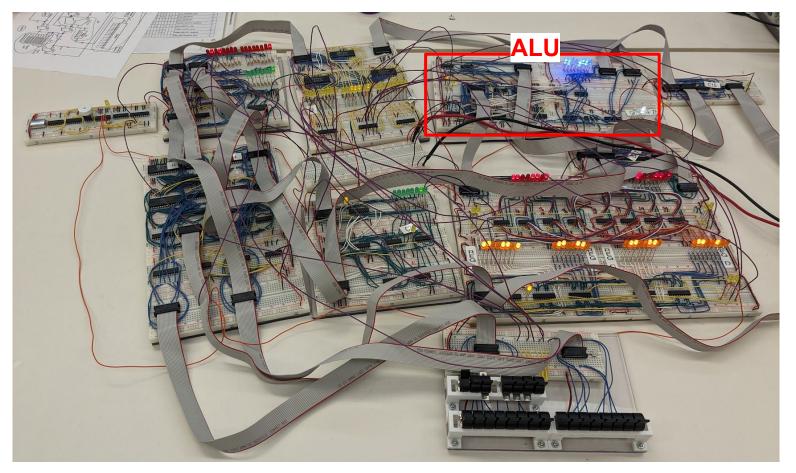

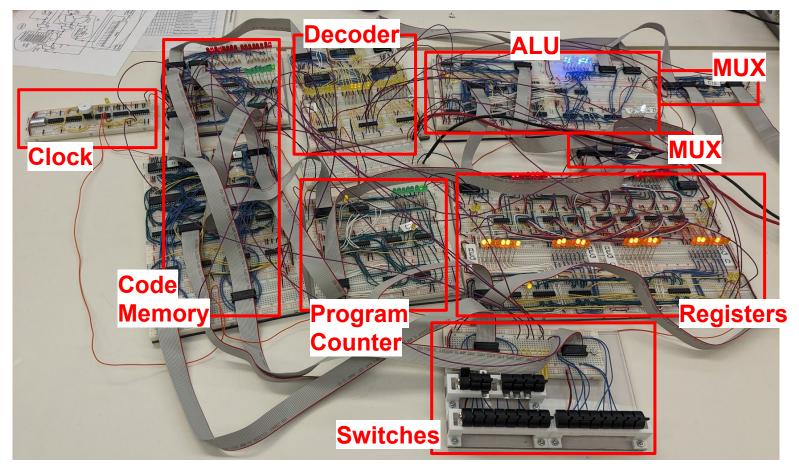

#### Where's the ALU?

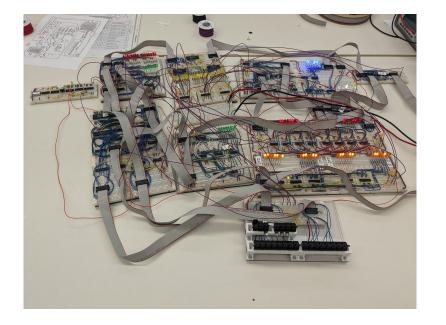

#### Minimum Viable Processor (Fall 2023)

312

#### **Expansion of the Original Design**

# i281CPU ⇒ i281*e* CPU

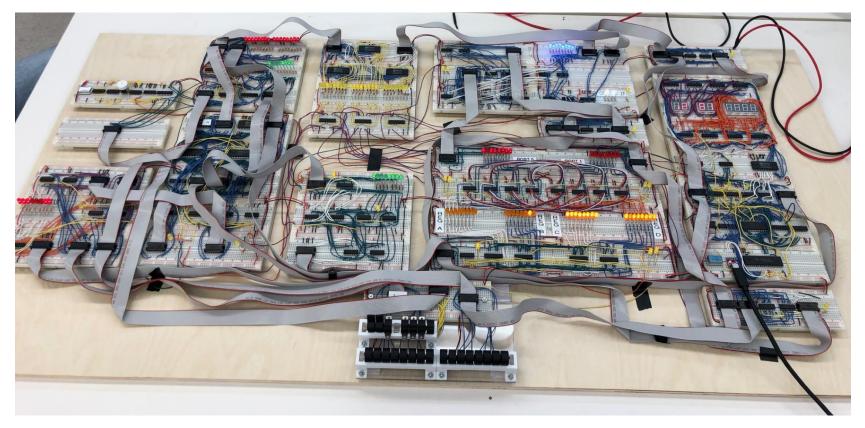

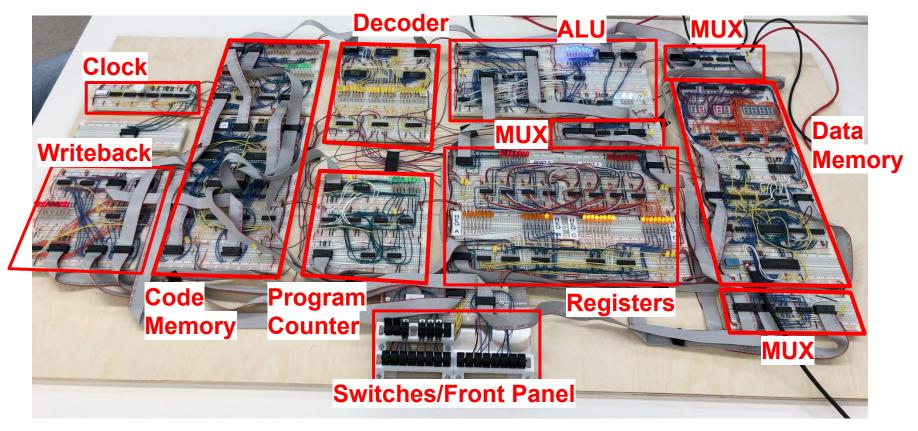

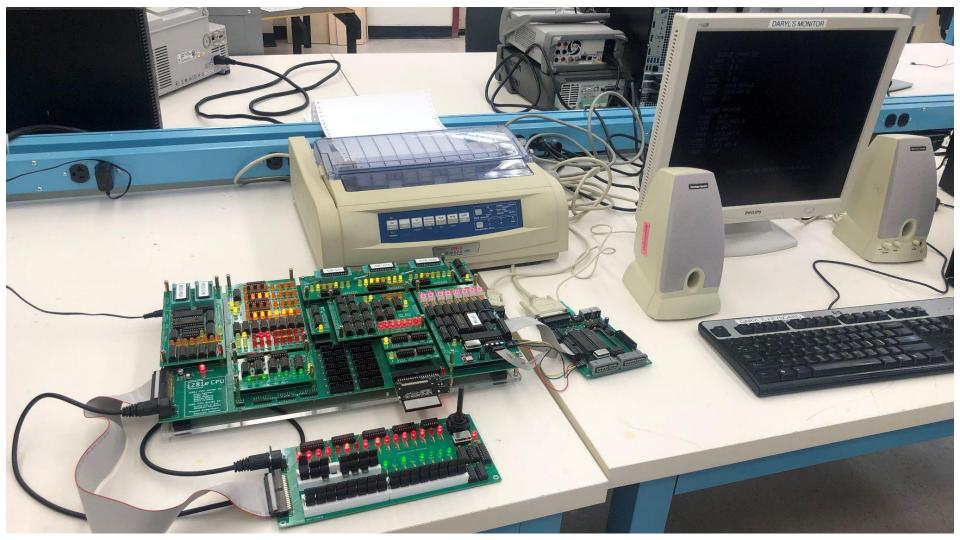

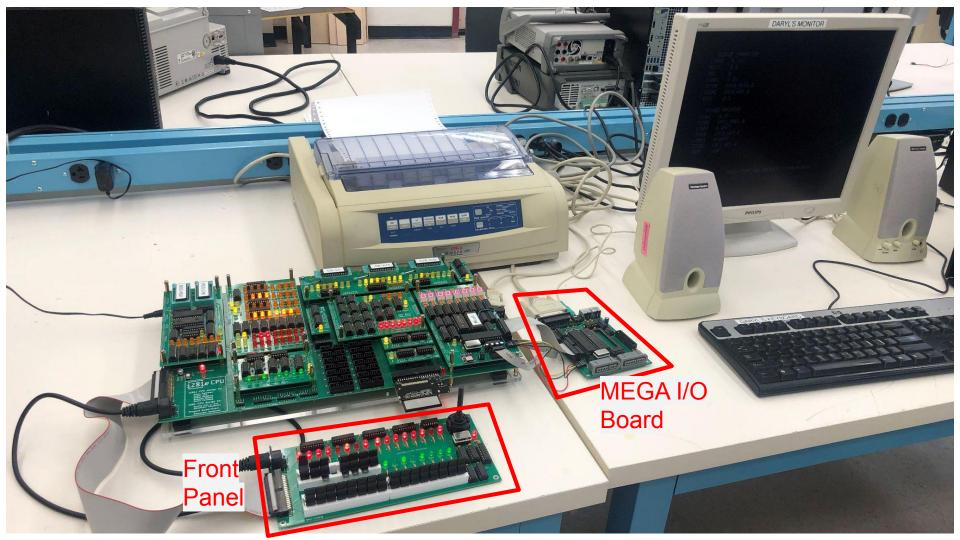

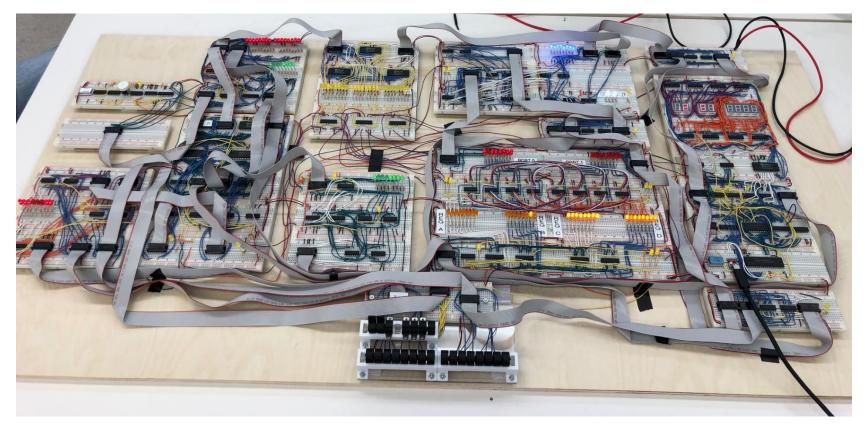

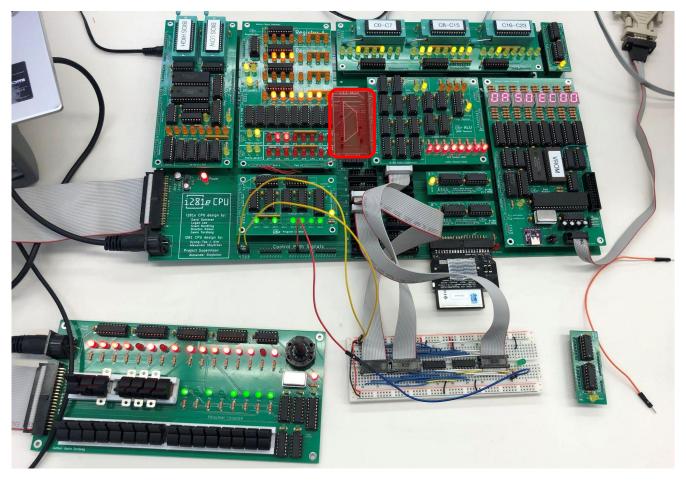

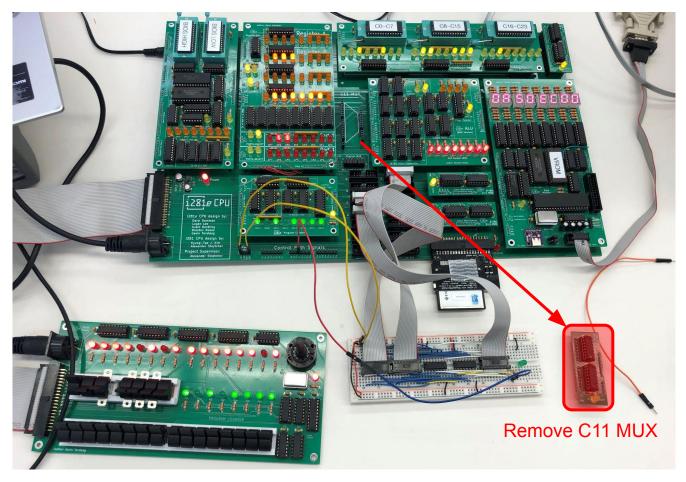

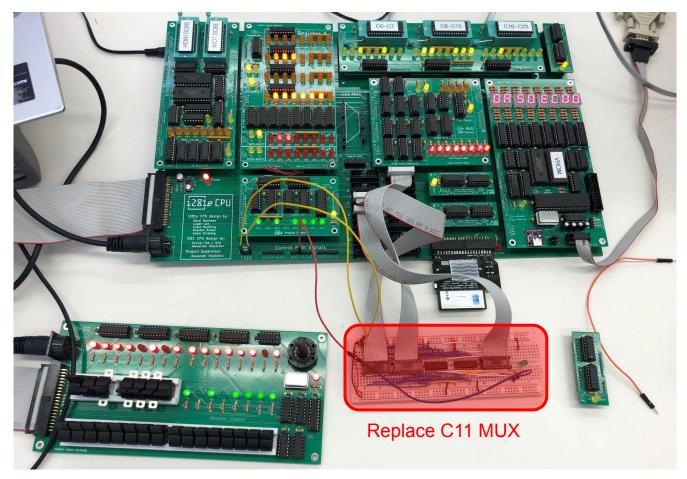

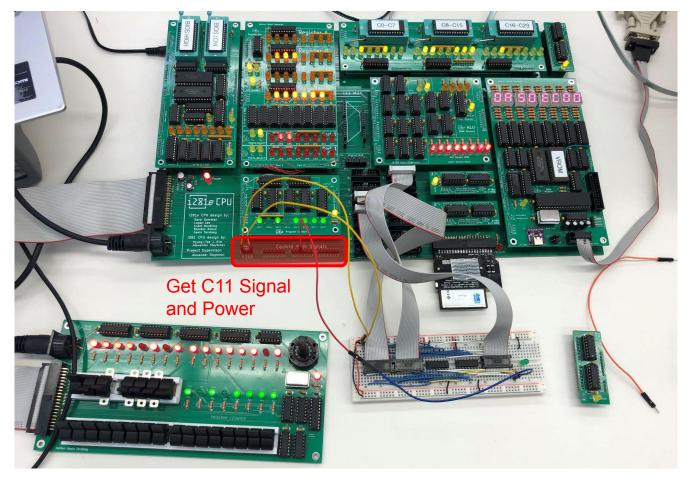

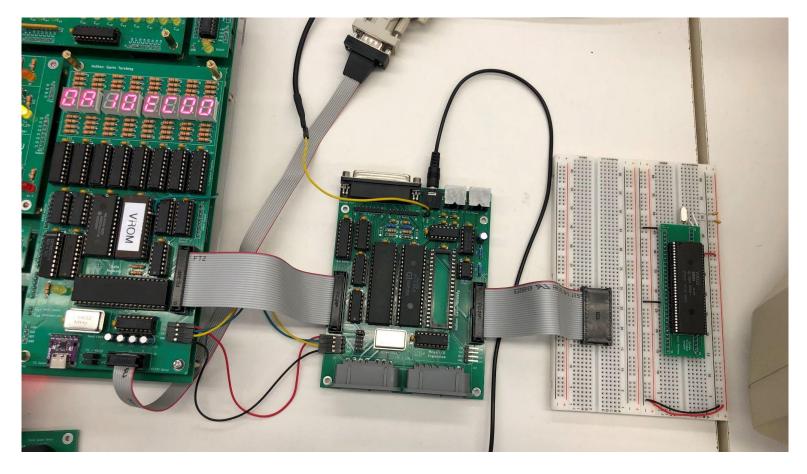

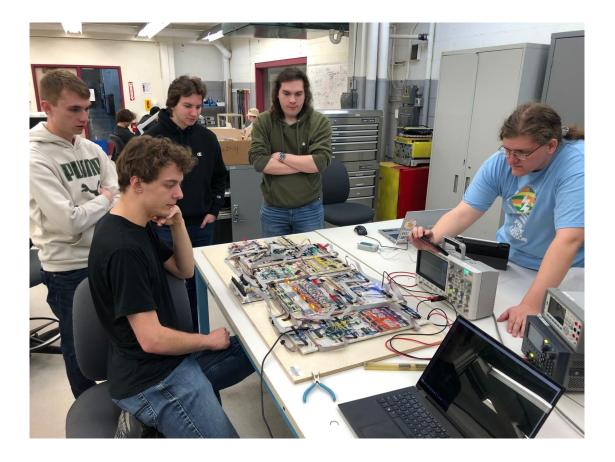

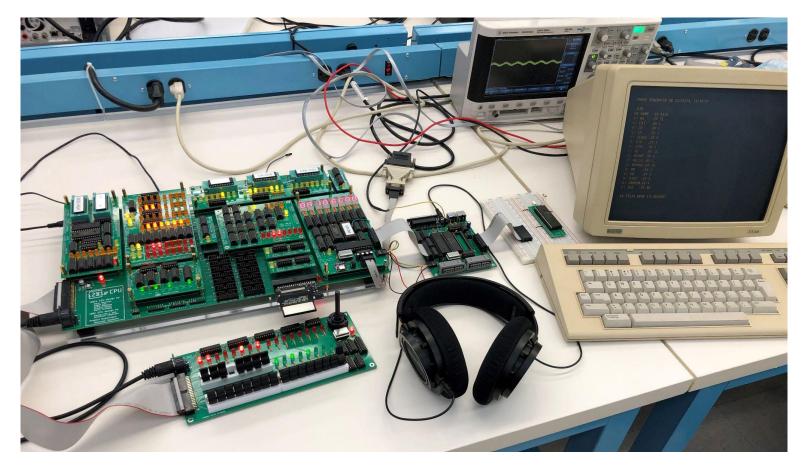

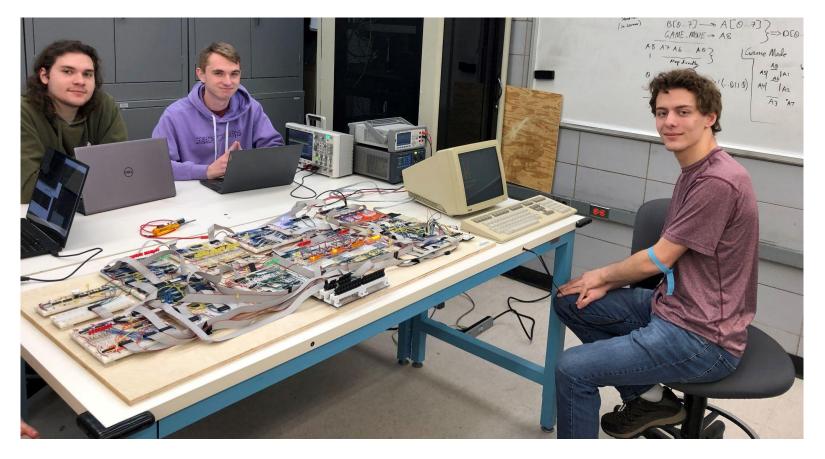

#### **Breadboard Machine (Early Spring 2024)**

#### **Breadboard Machine (Early Spring 2024)**

#### **Design Iterations**

#### **Design Iterations**

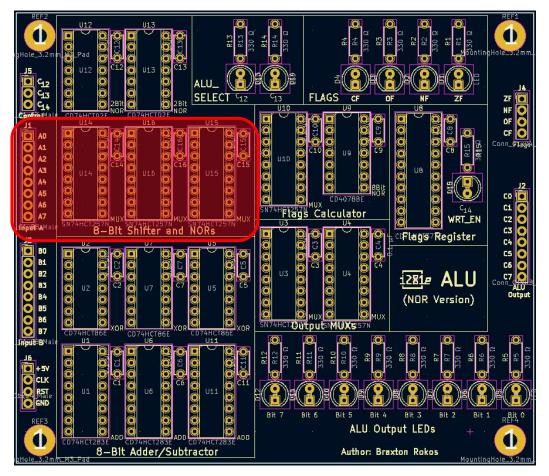

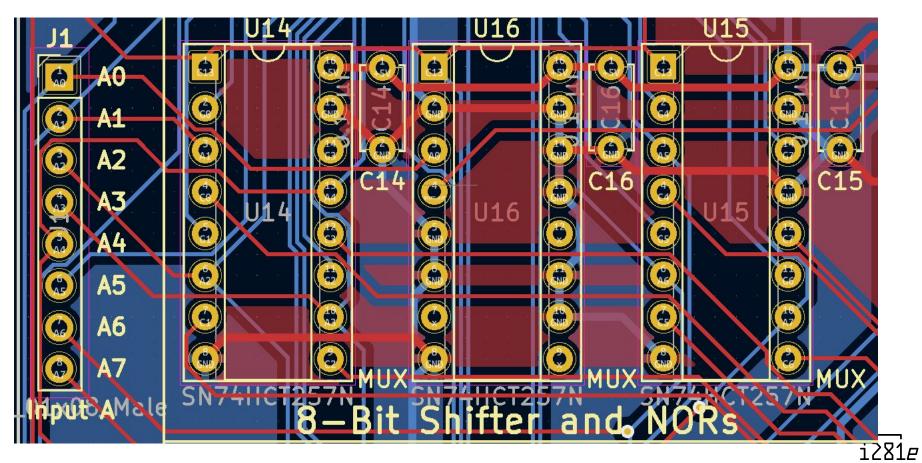

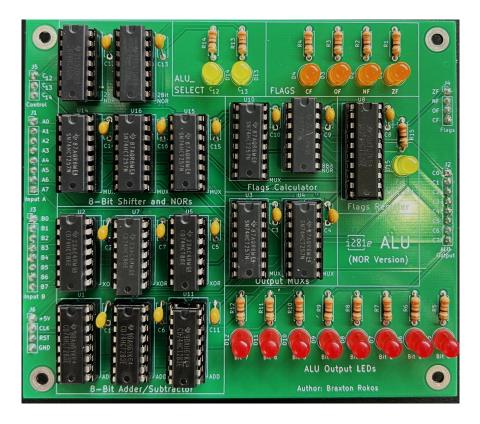

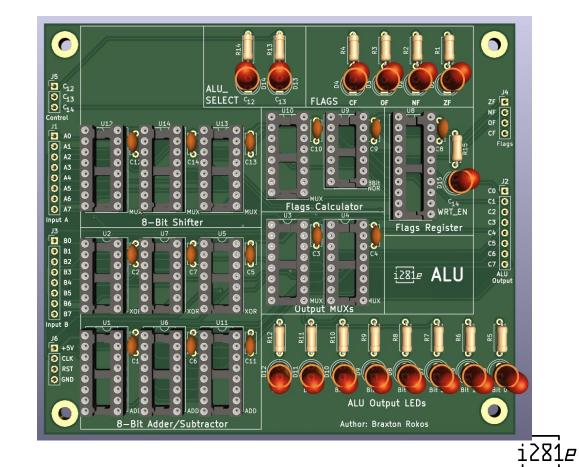

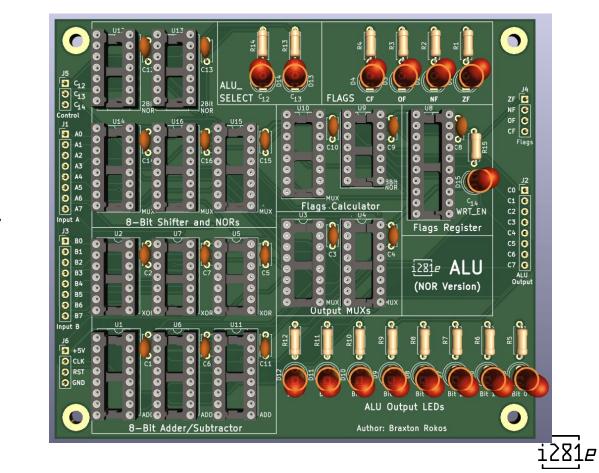

#### Let's look at the Arithmetic Logic Unit (ALU) again, for which we built two alternative PCB designs.

#### **ALU Logic**

#### **ALU Logic (NOR Version)**

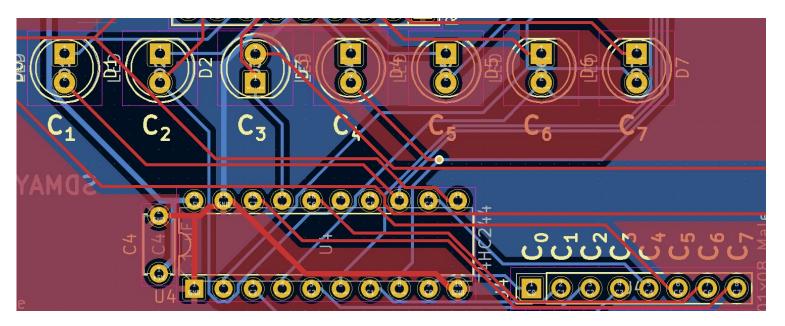

# **ALU Layout (First Version)**

### **ALU Layout (Second Version)**

### **ALU Layout (Second Version)**

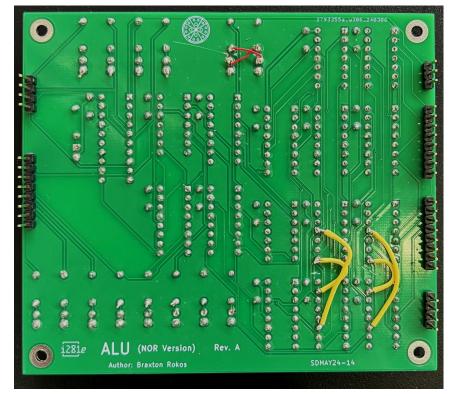

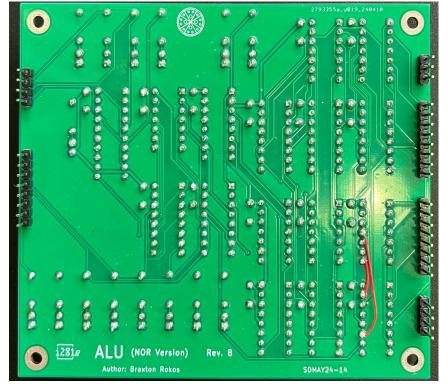

### **ALU Routing**

# **ALU PCB Implementation (Revision A)**

# **ALU PCB Implementation (Revision B)**

i281*e*

i281*e*

# **Technical Details**

Gavin Tersteeg Software Engineering

# **Loading User Programs**

Original i281 CPU

- "Magically" loads programs/BIOS into memory

- No boot sequence/procedures

- User program loading done by "external" mechanisms

New i281e CPU

- External program load mechanism too complex to physically implement

- System must be able to load its own programs

# **Expanded Memory**

#### Original i281 CPU

- 32 words Code ROM (BIOS)

- 32 words Code RAM

- 16 bytes Data Memory

No Mass Storage / Hard Disk

# **Expanded Memory**

Original i281 CPU

New i281e CPU

32 words - Code ROM (BIOS) => 128 words - Code ROM (BIOS)

32 words - Code RAM => 32 KW - Code RAM

16 bytes - Data Memory => 32 KB - Data Memory

No Mass Storage / Hard Disk => 32 MB

- Compact Flash Memory "Hard Disk"

### **Original Opcodes**

| NOOP    | NO OPeration                                       |

|---------|----------------------------------------------------|

| INPUTC  | INPUT into Code memory                             |

| INPUTCF | INPUT into Code memory with oFfset                 |

| INPUTD  | INPUT into Data memory                             |

| INPUTDF | <b>INPUT</b> into <b>Data memory with oFfset</b>   |

| MOVE    | MOVE the contents of one register into another     |

| LOADI   | LOAD Immediate value                               |

| LOADP   | LOAD Pointer address                               |

| ADD     | ADD two registers                                  |

| ADDI    | ADD an Immediate value to a register               |

| SUB     | SUBtract two registers                             |

| SUBI    | SUBtract an Immediate value from a register        |

| LOAD    | LOAD from a data memory address into a register    |

| LOADF   | LOAD with an oFfset specified by another register  |

| STORE   | STORE a register into a data memory address        |

| STOREF  | STORE with an oFfset specified by another register |

| SHIFTL  | SHIFT Left all bits in a register                  |

| SHIFTR  | SHIFT Right all bits in a register                 |

| CMP     | CoMPare the values in two registers                |

| JUMP    | JUMP unconditionally to a specified address        |

| BRE     | BRanch if Equal                                    |

| BRZ     | BRanch if Zero                                     |

| BRNE    | BRanch if Not Equal                                |

| BRNZ    | BRanch if Not Zero                                 |

| BRG     | BRanch if Greater                                  |

| BRGE    | BRanch if Greater than or Equal                    |

# **Original i281 Instruction Set Table**

|      | 0x-0                | 0x-1              | Øx-2              | 0x-3              | 0x-4              | 0x-5                | 0x-6              | 0x-7              | Øx-8              | 0x-9              | Øx-A                | Øx-B              | Øx-C              | Øx-D              | Øx-E              | Øx-F                |

|------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|

| 0x0- | NOOP                |                   |                   |                   |                   |                     |                   |                   |                   |                   |                     |                   |                   |                   |                   |                     |

| 0×1- | INPUTC [*]          | INPUTCF<br>[A+*]  | INPUTD [*]        | INPUTDF<br>[A+*]  |                   | INPUTCF<br>[B+*]    |                   | INPUTDF<br>[B+*]  |                   | INPUTCF<br>[C+*]  |                     | INPUTDF<br>[C+*]  |                   | INPUTCF<br>[D+*]  |                   | INPUTDF<br>[D+*]    |

| Øx2- | MOV A,A<br>NOOP     | MOV A,B           | MOV A,C           | MOV A,D           | MOV B,A           | MOV B,B<br>NOOP     | MOV B,C           | MOV B,D           | MOV C,A           | MOV C,B           | MOV C,C<br>NOOP     | MOV C,D           | MOV D,A           | MOV D,B           | MOV D,C           | MOV D,D<br>NOOP     |

| Øx3- | LOADI A,*           |                   |                   |                   | LOADI B,*         |                     |                   |                   | LOADI C,*         |                   |                     |                   | LOADI D,*         |                   |                   |                     |

| 0x4- | ADD A,A<br>SHIFTL A | ADD A,B           | ADD A,C           | ADD A,D           | ADD B,A           | ADD B,B<br>SHIFTL B | ADD B,C           | ADD B,D           | ADD C,A           | ADD C,B           | ADD C,C<br>SHIFTL C | ADD C,D           | ADD D,A           | ADD D,B           | ADD D,C           | ADD D,D<br>SHIFTL D |

| 0x5- | ADDI A,*            |                   |                   |                   | ADDI B,*          |                     |                   |                   | ADDI C,*          |                   |                     |                   | ADDI D,*          |                   |                   |                     |

| Øx6- | SUB A,A             | SUB A,B           | SUB A,C           | SUB A,D           | SUB B,A           | SUB B,B             | SUB B,C           | SUB B,D           | SUB C,A           | SUB C,B           | SUB C,C             | SUB C,D           | SUB D,A           | SUB D,B           | SUB D,C           | SUB D,D             |

| 0x7- | SUBI A,*            |                   |                   |                   | SUBI B,*          |                     |                   |                   | SUBI C,*          |                   |                     |                   | SUBI D,*          |                   |                   |                     |

| Øx8- | LOAD A,[*]          |                   |                   |                   | LOAD B,[*]        |                     |                   |                   | LOAD C,[*]        |                   |                     |                   | LOAD D,[*]        |                   |                   |                     |

| 0x9- | LOADF A,<br>[A+*]   | LOADF A,<br>[B+*] | LOADF A,<br>[C+*] | LOADF A,<br>[D+*] | LOADF B,<br>[A+*] | LOADF B,<br>[B+*]   | LOADF B,<br>[C+*] | LOADF B,<br>[D+*] | LOADF C,<br>[A+*] | LOADF C,<br>[B+*] | LOADF C,<br>[C+*]   | LOADF C,<br>[D+*] | LOADF D,<br>[A+*] | LOADF D,<br>[B+*] | LOADF D,<br>[C+*] | LOADF D,<br>[D+*]   |

| ØxA- | STORE<br>[*],A      |                   |                   |                   | STORE<br>[*],B    |                     |                   |                   | STORE<br>[*],C    |                   |                     |                   | STORE<br>[*],D    |                   |                   |                     |

| ØxB- | STOREF<br>[A+*],A   | STOREF<br>[B+*],A | STOREF<br>[C+*],A | STOREF<br>[D+*],A | STOREF<br>[A+*],B | STOREF<br>[B+*],B   | STOREF<br>[C+*],B | STOREF<br>[D+*],B | STOREF<br>[A+*],C | STOREF<br>[B+*],C | STOREF<br>[C+*],C   | STOREF<br>[D+*],C | STOREF<br>[A+*],D | STOREF<br>[B+*],D | STOREF<br>[C+*],D | STOREF<br>[D+*],D   |

| ØxC- | SHIFTL A            | SHIFTR A          |                   |                   | SHIFTL B          | SHIFTR B            |                   |                   | SHIFTL C          | SHIFTR C          |                     |                   | SHIFTL D          | SHIFTR D          |                   |                     |

| ØxD- | CMP A,A             | CMP A,B           | CMP A,C           | CMP A,D           | CMP B,A           | CMP B,B             | СМР В,С           | CMP B,D           | CMP C,A           | СМР С,В           | CMP C,C             | CMP C,D           | CMP D,A           | CMP D,B           | CMP D,C           | CMP D,D             |

| ØxE- | JUMP *              |                   |                   |                   |                   |                     |                   |                   |                   |                   |                     |                   |                   |                   |                   |                     |

| ØxF- | BRZ *<br>BRE *      | BRNZ *<br>BRNE *  | BRG *             | BRGE *            |                   |                     |                   |                   |                   |                   |                     |                   |                   |                   |                   |                     |

i281*e*

|      | 0x-0                | 0x-1              | 0x-2              | 0x-3              | 0x-4              | 0x-5                | 0x-6              | 0x-7              | 0x-8              | 0x-9              | 0x-A                | Øx-B              | 0x-C              | 0x-D              | 0x-E              | 0x-F                |

|------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|

| ×0-  | BANK A+*            |                   |                   |                   | BANK B+*          |                     |                   |                   | BANK C+*          |                   |                     |                   | BANK D+*          |                   |                   |                     |

| <1-  | INPUTC [*]          | INPUTCF<br>[A+*]  | INPUTD [*]        | INPUTDF<br>[A+*]  | CACHE A           | INPUTCF<br>[B+*]    | WRITE<br>[B+*],A  | INPUTDF<br>[B+*]  |                   | INPUTCF<br>[C+*]  | WRITE<br>[C+*],A    | INPUTDF<br>[C+*]  |                   | INPUTCF<br>[D+*]  | WRITE<br>[D+*],A  | INPUTDF<br>[D+*]    |

| (2-  | MOV A,A<br>NOOP     | MOV A,B           | MOV A,C           | MOV A,D           | MOV B,A           | MOV B,B<br>NOOP     | MOV B,C           | MOV B,D           | MOV C,A           | MOV C,B           | MOV C,C<br>NOOP     | MOV C,D           | MOV D,A           | MOV D,B           | MOV D,C           | MOV D,D<br>NOOP     |

| <3-  | LOADI A,*           |                   |                   |                   | LOADI B,*         |                     |                   |                   | LOADI C,*         |                   |                     |                   | LOADI D,*         |                   |                   |                     |

| <4-  | ADD A,A<br>Shiftl A | ADD A,B           | ADD A,C           | ADD A,D           | ADD B,A           | ADD B,B<br>SHIFTL B | ADD B,C           | ADD B,D           | ADD C,A           | ADD C,B           | ADD C,C<br>SHIFTL C | ADD C,D           | ADD D,A           | ADD D,B           | ADD D,C           | ADD D,D<br>SHIFTL D |

| <5-  | ADDI A,*            |                   |                   |                   | ADDI B,*          |                     |                   |                   | ADDI C,*          |                   |                     |                   | ADDI D,*          |                   |                   |                     |

| <6-  | SUB A,A             | SUB A,B           | SUB A,C           | SUB A,D           | SUB B,A           | SUB B,B             | SUB B,C           | SUB B,D           | SUB C,A           | SUB C,B           | SUB C,C             | SUB C,D           | SUB D,A           | SUB D,B           | SUB D,C           | SUB D,D             |

| <7-  | SUBI A,*            |                   |                   |                   | SUBI B,*          |                     |                   |                   | SUBI C,*          |                   |                     |                   | SUBI D,*          |                   |                   |                     |

| <8-  | LOAD A,[*]          |                   |                   |                   | LOAD B,[*]        |                     |                   |                   | LOAD C,[*]        |                   |                     |                   | LOAD D,[*]        |                   |                   |                     |

| (9-  | LOADF A,<br>[A+*]   | LOADF A,<br>[B+*] | LOADF A,<br>[C+*] | LOADF A,<br>[D+*] | LOADF B,<br>[A+*] | LOADF B,<br>[B+*]   | LOADF B,<br>[C+*] | LOADF B,<br>[D+*] | LOADF C,<br>[A+*] | LOADF C,<br>[B+*] | LOADF C,<br>[C+*]   | LOADF C,<br>[D+*] | LOADF D,<br>[A+*] | LOADF D,<br>[B+*] | LOADF D,<br>[C+*] | LOADF D,<br>[D+*]   |

| κA-  | STORE<br>[*],A      |                   |                   |                   | STORE<br>[*],B    |                     |                   |                   | STORE<br>[*],C    |                   |                     |                   | STORE<br>[*],D    |                   |                   |                     |

| сB-  | STOREF<br>[A+*],A   | STOREF<br>[B+*],A | STOREF<br>[C+*],A | STOREF<br>[D+*],A | STOREF<br>[A+*],B | STOREF<br>[B+*],B   | STOREF<br>[C+*],B | STOREF<br>[D+*],B | STOREF<br>[A+*],C | STOREF<br>[B+*],C | STOREF<br>[C+*],C   | STOREF<br>[D+*],C | STOREF<br>[A+*],D | STOREF<br>[B+*],D | STOREF<br>[C+*],D | STOREF<br>[D+*],D   |

| ĸC-  | NORI A,*            | SHIFTR A          |                   |                   | NORI B,*          | SHIFTR B            |                   |                   | NORI C,*          | SHIFTR C          |                     |                   | NORI D,*          | SHIFTR D          |                   |                     |

| ۲D-  | CMP A,A             | CMP A,B           | CMP A,C           | CMP A,D           | CMP B,A           | CMP B,B             | CMP B,C           | CMP B,D           | CMP C,A           | CMP C,B           | CMP C,C             | CMP C,D           | CMP D,A           | CMP D,B           | CMP D,C           | CMP D,D             |

| κE-  | NOR A,A             | NOR A,B           | NOR A,C           | NOR A,D           | NOR B,A           | NOR B,B             | NOR B,C           | NOR B,D           | NOR C,A           | NOR C,B           | NOR C,C             | NOR C,D           | NOR D,A           | NOR D,B           | NOR D,C           | NOR D,D             |

| ĸF - | BRC *<br>BRAE *     | BRNC *<br>BRB *   | BRO *             | BRNO *            | BRN *             | BRNN *<br>BRP *     | BRZ *<br>BRE *    | BRNZ *<br>BRNE *  | BRA *             | BRBE *            | BRG *               | BRGE *            | BRL *             | BRLE *            | JUMPR C+*         | JUMP *              |

# **Expanded i281e Instruction Set Table**

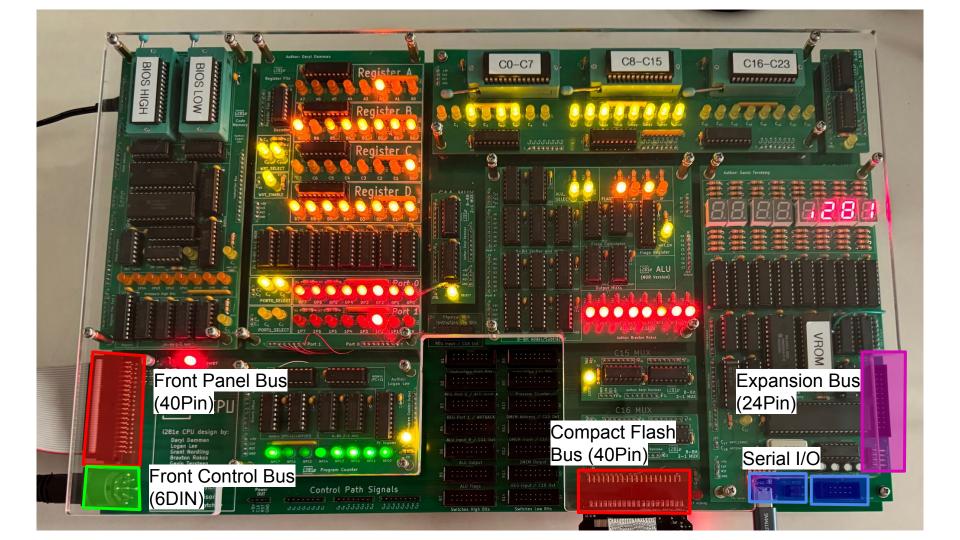

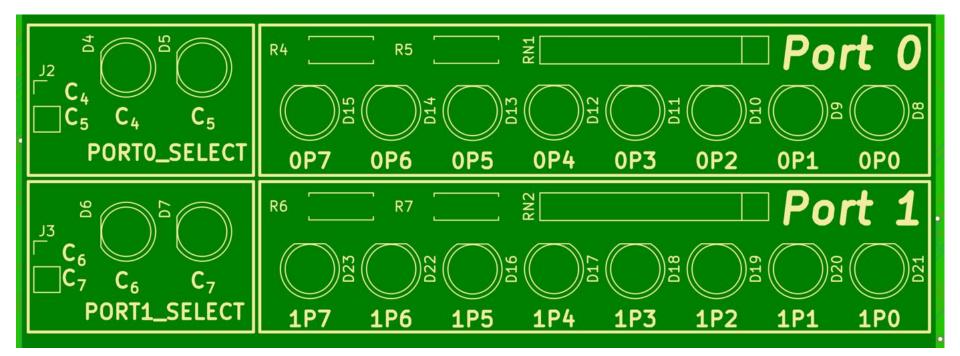

# **External Connectors**

- Front Panel / Control Bus

- 40-Pin IDC and 6-Pin DIN for providing clock and switch controls

- Serial I/O

- TTL-Logic or RS-232 serial connection to on-board UART (for DOS/281 or MONITOR)

- Compact Flash

- "Hard Disk" of the system, using Compact Flash bus protocols

- Expansion Bus

- Smaller version of S-100 Bus (IEEE-696) connection for managing external peripherals

#### What's left?

- Expanded memory allows for boot software to execute

- i281e CPU can now directly access mass storage to read programs

- New opcodes to take data and automatically write it to memory

#### What's left?

- Expanded memory allows for boot software to execute

- i281e CPU can now directly access mass storage to read programs

- New opcodes to take data and automatically write it to memory

#### All that remains now is the software.

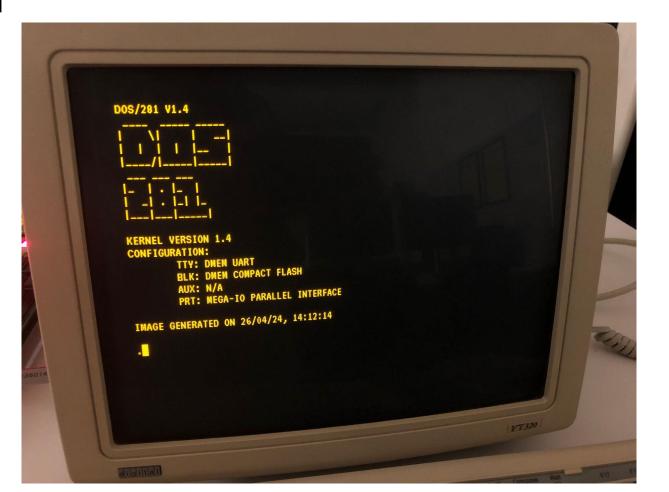

### DOS/281

# **DOS/281** Features

- Loading user programs

- Downloading and saving new user programs

- Managing program and non-program files on the compact flash card

- Allowing editing, assembly, and debugging of user programs locally

- Providing API interfaces for more complex i281 applications

DOS/281 is implemented in ~3,000 lines of assembly code, and occupies 5 KB of memory.

This is about **0.011%** of the size of the Linux kernel.

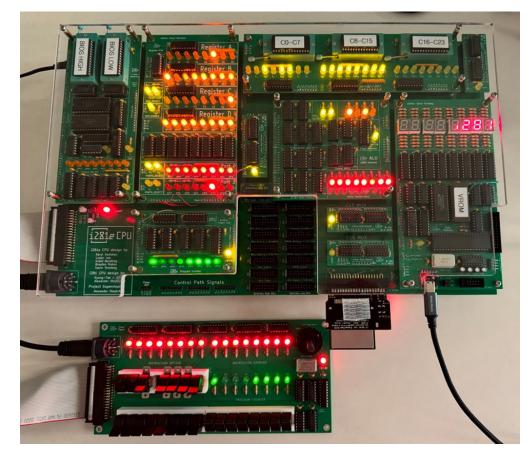

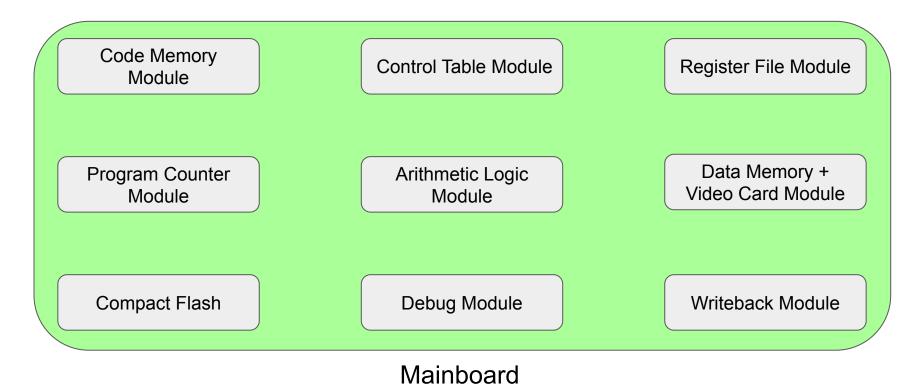

# Expandability

Gavin Tersteeg Software Engineering

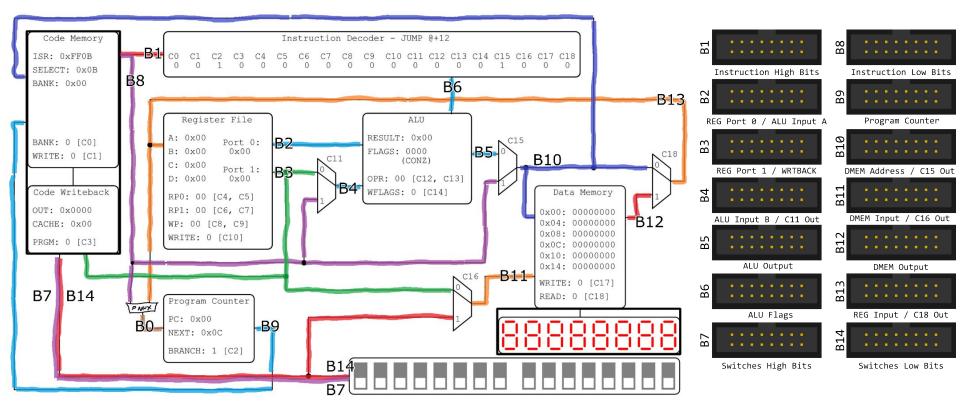

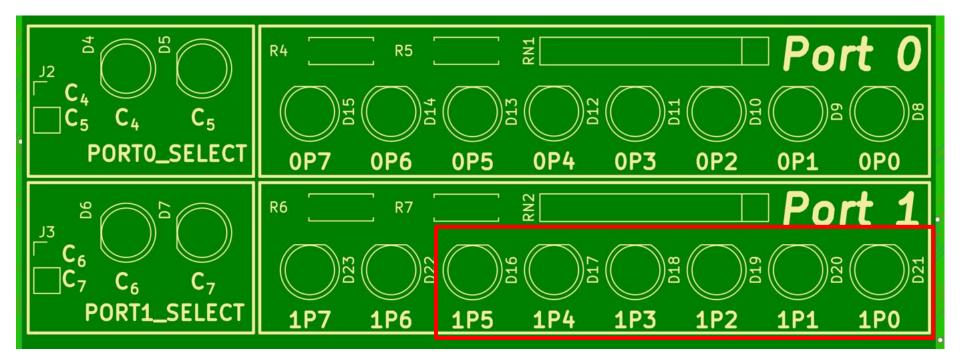

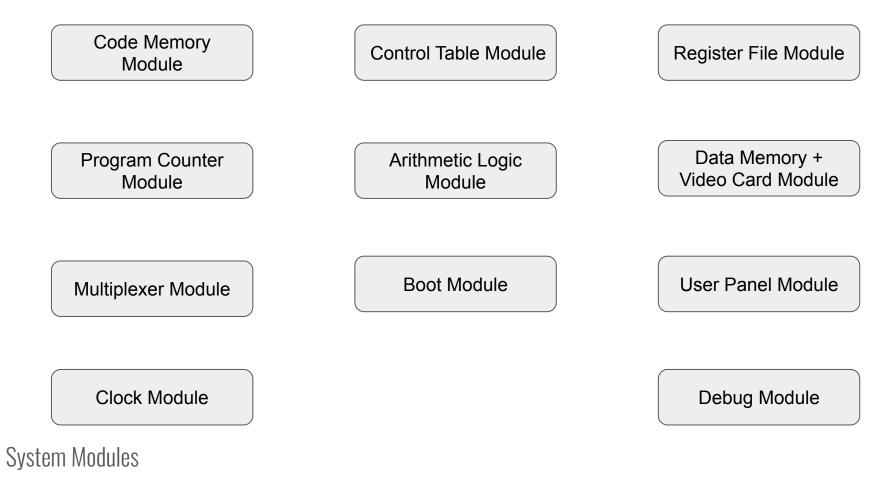

#### Each Ribbon Cable is an 8-bit Bus

# **Module Separation**

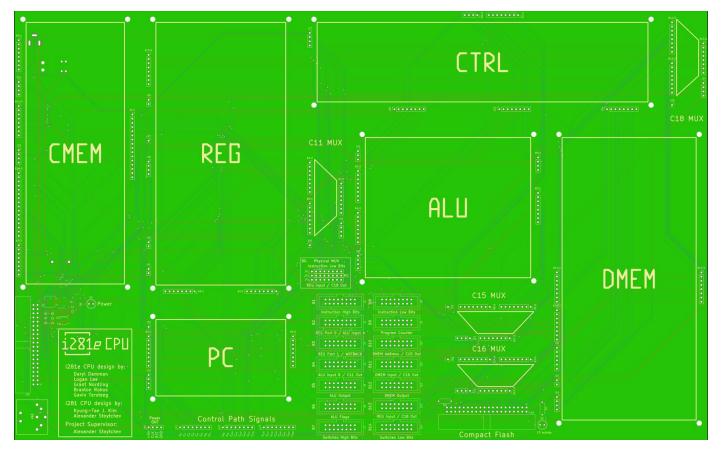

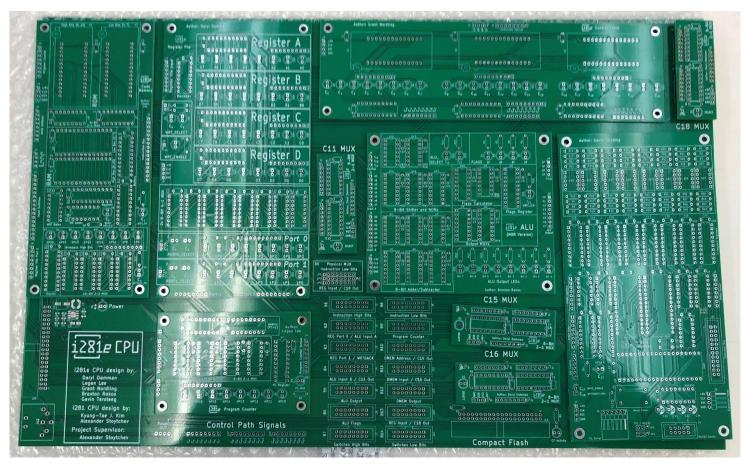

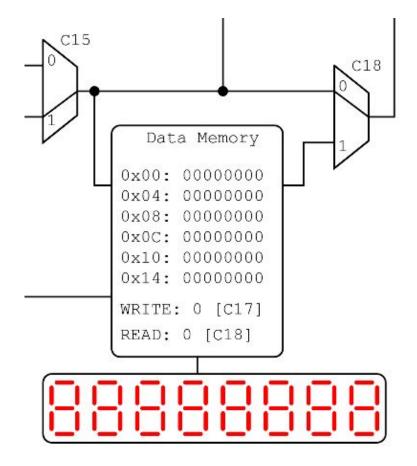

# **Mainboard PCB Diagram**

# Two Layer Design

i281*e*

#### **Mainboard Bus Connectors**

#### **Expansion Capability**

## Testing

Braxton Rokos Electrical Engineering

#### **Breadboard Testing**

1*P*

#### **Breadboard Stability**

#### **PCB** Testing

- Self-Check Program for Several Opcodes

- Reassurances Testing

- Power Analysis

- Clock Frequency Limit Tests

- Verification Testing

- Full System Integration Testing

- Comparing Simulator Results to Hardware Results

## **Lessons Learned**

Grant Nordling Electrical Engineering

#### **Circuit Validation**

#### **PCB** Routing

#### **Fixing PCBs: Inverted Select Bit fixed with NOT gate IC**

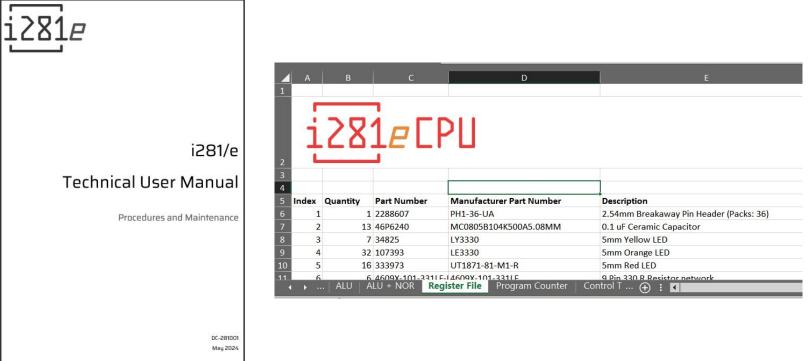

#### **Documentation & Bill of Materials**

#### Acknowledgements

- Matt Post, Lee Harker, and ETG Student Staff

- ECPE Department

- Dr. Alexander Stoytchev

#

# Discover the *extended* difference.

# **Questions?**

### THE END

## **Backup Slides**

#### **Mainboard Bus Connectors**

| Expanded i281e | Instruction | Set Table |

|----------------|-------------|-----------|

|----------------|-------------|-----------|

|      | 0x-0                | 0x-1              | 0x-2              | 0x-3              | 0x-4              | 0x-5                | 0x-6              | 0x-7              | 0x-8              | 0x-9              | Øx-A                | Øx-B              | Øx-C              | 0x-D              | Øx-E              | Øx-F                |

|------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|-------------------|---------------------|

| 0×0- | BANK A+*            |                   |                   |                   | BANK B+*          |                     |                   |                   | BANK C+*          |                   |                     |                   | BANK D+*          |                   |                   |                     |

| 0×1- | INPUTC [*]          | INPUTCF<br>[A+*]  | INPUTD [*]        | INPUTDF<br>[A+*]  | CACHE A           | INPUTCF<br>[B+*]    | WRITE<br>[B+*],A  | INPUTDF<br>[B+*]  |                   | INPUTCF<br>[C+*]  | WRITE<br>[C+*],A    | INPUTDF<br>[C+*]  |                   | INPUTCF<br>[D+*]  | WRITE<br>[D+*],A  | INPUTDF<br>[D+*]    |

| 0x2- | MOV A,A<br>NOOP     | MOV A,B           | MOV A,C           | MOV A,D           | MOV B,A           | MOV B,B<br>NOOP     | MOV B,C           | MOV B,D           | MOV C,A           | MOV C,B           | MOV C,C<br>NOOP     | MOV C,D           | MOV D,A           | MOV D,B           | MOV D,C           | MOV D,D<br>NOOP     |

| 0x3- | LOADI A,*           |                   |                   |                   | LOADI B,*         |                     |                   |                   | LOADI C,*         |                   |                     |                   | LOADI D,*         |                   |                   |                     |

| 0×4- | ADD A,A<br>Shiftl A | ADD A,B           | ADD A,C           | ADD A,D           | ADD B,A           | ADD B,B<br>SHIFTL B | ADD B,C           | ADD B,D           | ADD C,A           | ADD C,B           | ADD C,C<br>SHIFTL C | ADD C,D           | ADD D,A           | ADD D,B           | ADD D,C           | ADD D,D<br>Shiftl D |

| 0×5- | ADDI A,*            |                   | 222               |                   | ADDI B,*          | <u>1997</u>         |                   |                   | ADDI C,*          | <u>444</u>        |                     |                   | ADDI D,*          | 2222              |                   | 10<br><u></u>       |

| 0×6- | SUB A,A             | SUB A,B           | SUB A,C           | SUB A,D           | SUB B,A           | SUB B,B             | SUB B,C           | SUB B,D           | SUB C,A           | SUB C,B           | SUB C,C             | SUB C,D           | SUB D,A           | SUB D,B           | SUB D,C           | SUB D,D             |

| 0x7- | SUBI A,*            |                   |                   |                   | SUBI B,*          |                     |                   |                   | SUBI C,*          |                   |                     |                   | SUBI D,*          |                   |                   |                     |

| 0×8- | LOAD A,[*]          |                   |                   |                   | LOAD B,[*]        |                     |                   |                   | LOAD C,[*]        |                   |                     |                   | LOAD D,[*]        |                   |                   |                     |

| 0×9- | LOADF A,<br>[A+*]   | LOADF A,<br>[B+*] | LOADF A,<br>[C+*] | LOADF A,<br>[D+*] | LOADF B,<br>[A+*] | LOADF B,<br>[B+*]   | LOADF B,<br>[C+*] | LOADF B,<br>[D+*] | LOADF C,<br>[A+*] | LOADF C,<br>[B+*] | LOADF C,<br>[C+*]   | LOADF C,<br>[D+*] | LOADF D,<br>[A+*] | LOADF D,<br>[B+*] | LOADF D,<br>[C+*] | LOADF D,<br>[D+*]   |

| 0xA- | STORE<br>[*],A      |                   |                   |                   | STORE<br>[*],B    |                     |                   |                   | STORE<br>[*],C    |                   |                     |                   | STORE<br>[*],D    |                   |                   |                     |

| Øx₿- | STOREF<br>[A+*],A   | STOREF<br>[B+*],A | STOREF<br>[C+*],A | STOREF<br>[D+*],A | STOREF<br>[A+*],B | STOREF<br>[B+*],B   | STOREF<br>[C+*],B | STOREF<br>[D+*],B | STOREF<br>[A+*],C | STOREF<br>[B+*],C | STOREF<br>[C+*],C   | STOREF<br>[D+*],C | STOREF<br>[A+*],D | STOREF<br>[B+*],D | STOREF<br>[C+*],D | STOREF<br>[D+*],D   |

| ØxC- | NORI A,*            | SHIFTR A          |                   |                   | NORI B,*          | SHIFTR B            |                   |                   | NORI C,*          | SHIFTR C          |                     |                   | NORI D,*          | SHIFTR D          |                   |                     |

| 0xD- | CMP A,A             | СМР А,В           | CMP A,C           | CMP A,D           | CMP B,A           | CMP B,B             | CMP B,C           | CMP B,D           | CMP C,A           | CMP C,B           | CMP C,C             | CMP C,D           | CMP D,A           | CMP D,B           | CMP D,C           | CMP D,D             |

| ØxE- | NOR A,A             | NOR A,B           | NOR A,C           | NOR A,D           | NOR B,A           | NOR B,B             | NOR B,C           | NOR B,D           | NOR C,A           | NOR C,B           | NOR C,C             | NOR C,D           | NOR D,A           | NOR D,B           | NOR D,C           | NOR D,D             |

| 0xF- | BRC *<br>BRAE *     | BRNC *<br>BRB *   | BRO *             | BRNO *            | BRN *             | BRNN *<br>BRP *     | BRZ *<br>BRE *    | BRNZ *<br>BRNE *  | BRA *             | BRBE *            | BRG *               | BRGE *            | BRL *             | BRLE *            | JUMPR C+*         | JUMP *              |

#### **Adjustable Clock**

Adjustable CPU clock to enable stepping through individual instructions and operating at different clock frequencies.

#### **Expansion Capability**

#### Mainboard PCB with Overlaid Modules

#### **Project Vision**

The i281 CPU was designed to support the curriculum in CprE 281: Digital Logic. The CPU has no physical form capable of creating hands-on experiences for students. The CPU must be created in hardware and be similar to the FPGA and Simulator designs. The project consists of two stages: Breadboard and Printed Circuit Board. The Breadboard version must be created first to prove the concept and debug any issues. The Printed Circuit Board version will use the designs from the Breadboard version and implement them in a fashion that is easier to reproduce and learn from.

#### **Project Vision**

The students in the CPR E 281 digital logic course lack a physical design of an i281 CPU they can use to apply their learning.

When we originally laid out the curriculum, there were three classes (X81). The motivation for the project is to better prepare students for 381; however, after all these projects, etc. it was determined the students have no idea how to use breadboards and PCB. There does not exist material and a fully-fledged physical computer for 481, a non-existent class.

This processor is meant to be a sandbox to allow computer engineering students learn digital design experience. Used as a teaching platform for both 281 and 481. The original design is mysterious. This design takes way the confusion and showcases the internals in full.

The CPR E 281 Digital Logic Course demonstrates the i281 CPU on both FPGA and Simulators, yet lacks a hardware implementation of it. This project aims to physically build the hardware version of the design to emphasize the branch between software and hardware. - Braxton :)

#### **Breadboard Machine (Early Spring 2024)**

#### **FPGA Implementation (Summer 2019)**

#### i281 CPU covered in CprE 281 labs (Fall 2019 — Present)

#### i281 CPU covered in CprE 281 lectures (Fall 2019 — Present)

#### **Mindful Layout & Silkscreen**

#### i281 CPU Web Simulator (Spring 2021 — Present)

#### i281 CPU Web Simulator (Finished in Spring 2021)

#### **Our Project i281e CPU (Spring 2024)**

31*P*

#### **Mindful Layout**

#### **Expansion Capability**

#### Web Simulator for the i281e CPU

#### Web Simulator for the i281e CPU

#### Banking

Using banking techniques

Accessible Memory:

- 32 Kw Code Memory => 256 Banks Code Memory

- 32 KB Data Memory => 256 Banks Data Memory

- 32 MB Compact Flash (CF) Memory => 65,536 Blocks CF Memory

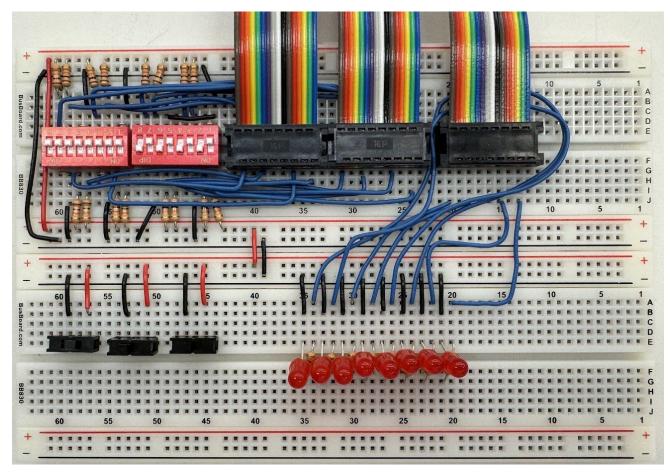

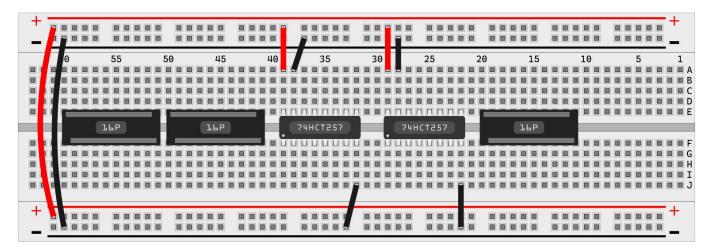

CPU data path and control path must be visualized through LEDs.

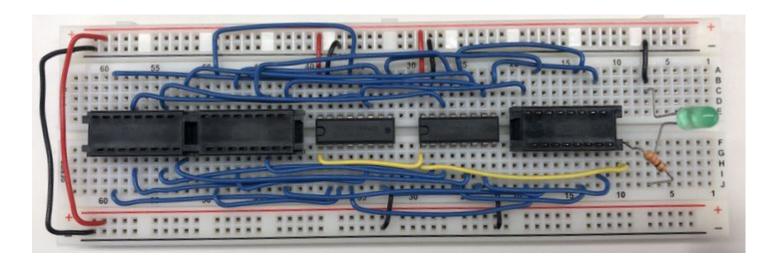

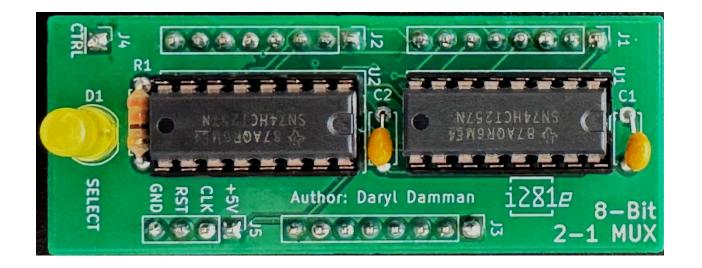

- After the logical schematic is finished, it must be translated into something that can be built on a breadboard.

- A rough component outline of each module is created before physical assembly can begin.

- Once a breadboard layout is finished, it can be physically implemented.

- Ribbon cable is used with the black connectors to transfer data across modules.

- PCB info?

- Mention how it connects to the Mainboard?

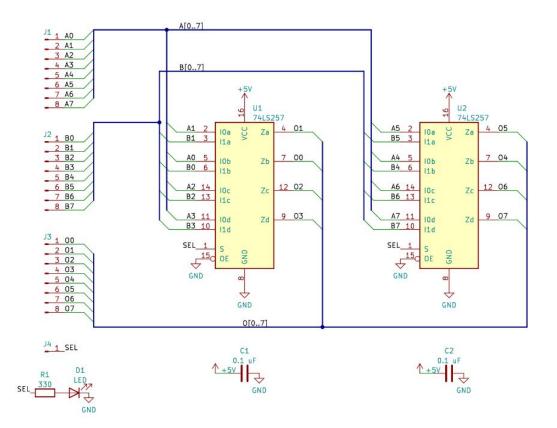

- Each module starts as a chip-level electrical schematic.

- Pictures is the schematic for the MUX

#### **Unadded Opcodes (Blue)**

|              | Signed                                    | VS           | Unsigned                                  |

|--------------|-------------------------------------------|--------------|-------------------------------------------|

| BRE<br>BRZ   | BRanch if Equal<br>BRanch if Zero         | BRE<br>BRZ   | Ranch if Equal<br>BRanch if Zero          |

| BRNE<br>BRNZ | BRanch if Not Equal<br>BRanch if Not Zero | BRNE<br>BRNZ | BRanch if Not Equal<br>BRanch if Not Zero |

| BRG          | BRanch if Greater                         | BRA          | BRanch if Above                           |

| BRGE         | BRanch if Greater than or Equ             | al BRAE      | BRanch if Above or Equal                  |

| BRL          | BRanch if Less                            | BRB          | BRanch if Below                           |

| BRLE         | BRanch if Less than or Equal              | BRBE         | BRanch if Below or Equal                  |

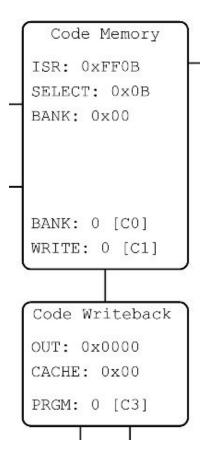

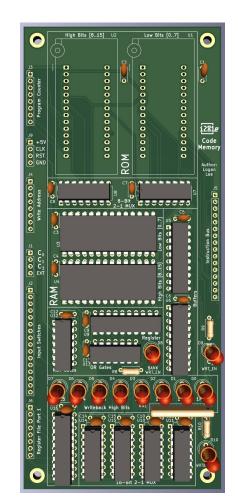

#### **Code Memory**

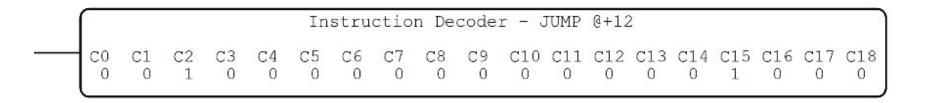

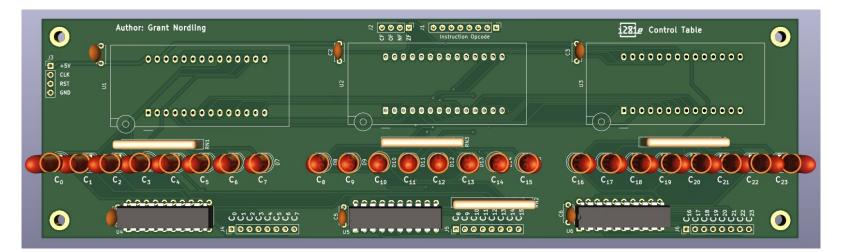

#### **Control Table / Instruction Decoder**

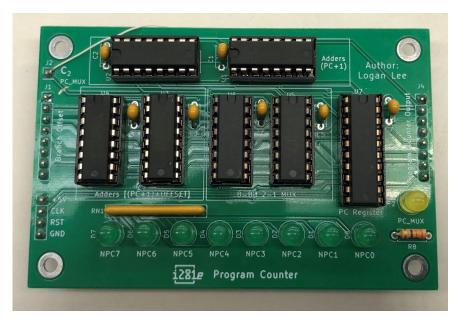

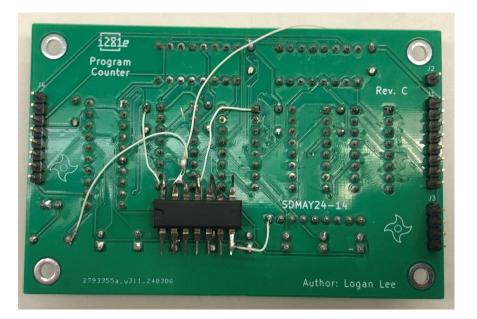

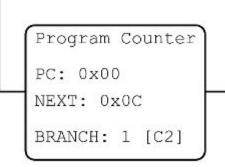

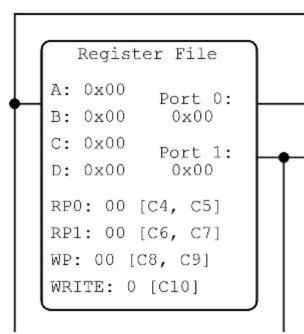

#### **Program Counter**

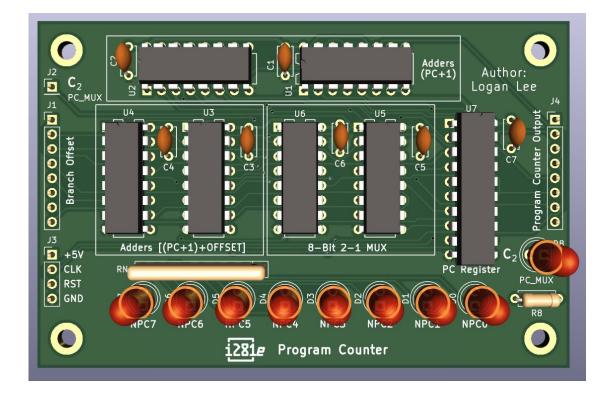

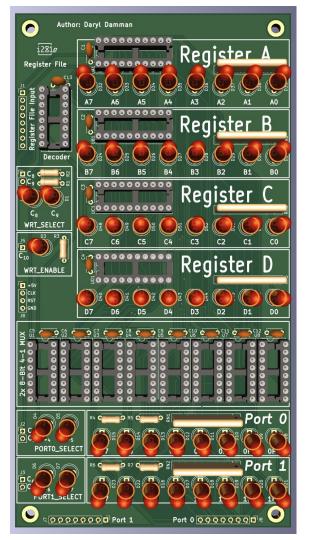

#### **Register File**

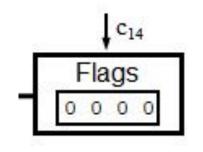

#### **ALU with Flags Register**

### ALU (NOR version)

#### **Flags Register**

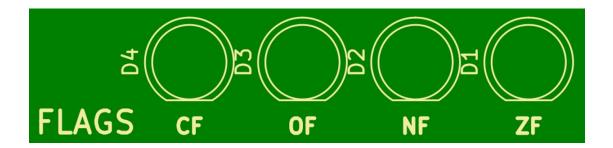

### **Data Memory and Video Card**

i281*e*

#### ALU Schematic (2 of 3)

#### ALU Schematic (3 of 3)

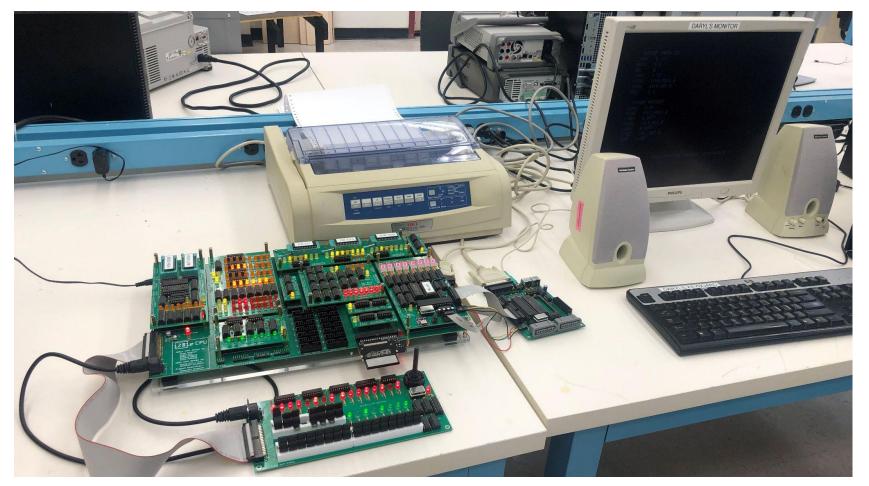

### Prototyping

- Since this project is more implementation heavy, most of our first semester was focused on constructing our prototype.

- The project requirements call for the first version of the i281 CPU to be built on solderless breadboards. This allowed us to build each module and test as we progressed.

- When an issue with a module was found, it could easily be corrected, and it's KiCAD design schematics updated.

#### **Prototype Implementations**

- As the semester progressed, we implemented enough of the prototype modules that we were able to construct a minimally viable processor (MVP).

- The MVP lacks a number of features that will be present on the finished product, but it allows most of the critical modules to be integration tested using simple test programs.

### Test Plan

#### • Acceptance Testing

- Testing electrical properties

- Ex. short circuits

#### • Integration Testing

• Entire system testing & running program

#### • Interface Testing

• Interface panel designed with basic input and control switches

#### **Breadboard Implementation**

## **Design Complexity**

- Breadboards and Wires

- Hardware

- Design/Constraints

- Limited By Breadboards

- Wiring Complexity

- Educational Emphasis

- Obtainable Parts

- Available parts

### **Design Iterations**

- i281 CPU Simulation and FPGA Design

- FPGA Design + Our

Design Decisions

- Fixed Errors From

Debugging & Redesigns

#### Project Schedule First Semester

- First Metric

- Initial Designs

- First Milestone

- Hardware Level Design

#### Project Schedule First Semester

- Second Metric

- Breadboards (BB)

- Second Milestone

- Breadboard Implementation

#### i281 CPU Project Timeline - First Semester 1-Sep-23 22-Sep-23 13-Oct-23 3-Nov-23 24-Nov-23 15-Dec-23 Breadboard Implementation MUXs (BB) Code Memory (BB) Program Counter (BB) PC Update Logic (BB) ALU (BB) Flag Register (BB) Register Files (BB) Interface Box (BB) Control Table (BB) Bus Management (BB) Power Management (BB) Control Line Mangement (BB) Data Memory (BB) Video Card (BB) Clock (BB)

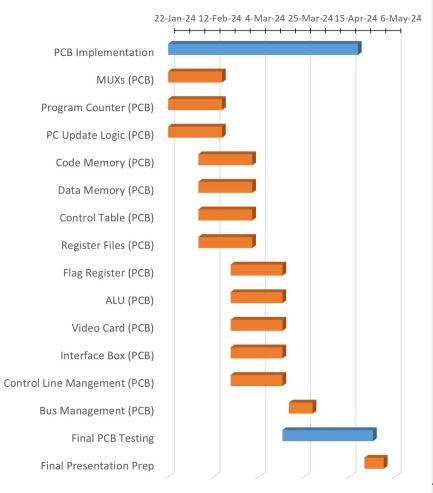

#### Project Schedule Second Semester

- Metric

- Printed Circuit Board (PCB)

#### • Milestones

- PCB Implementation

- Final PCB Testing

#### i281 CPU Project Timeline - Second Semester

# THE END++